Многоканальный преобразователь "частота-код"

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (») 57(.)186 (61) Дополнительное к авт. свид-ву

1 (22) Заявлено 14.02.74 (21) 1996863/2 1 (Я) М. Кл,й

Н 03 К 13/20 с присоединением заявки ¹(23) Приоритет (43) Опубликовано25.08.77, Бюллетень № 31 (4б) Дата опубликования описания 27.09.77

Гесударстввнный «си«тат

Севвта Минн«трав СССР сз дезам «зсбрвтсей н ст«рмт«й (53) УДК 621.317.761 (088.8) Г. М Власенко, В. Е. Евстигнеев, Е. М. Исаченков, и Б. М. Рачков (72) Авторы изобретения (Tl) Заявитель (54) МНОГОКАНАЛЬНЫЙ ПРЕОБРАЗОВА П:ЛЬ

ЧАСТОТА-KOjl

Изобретение относится к устройствам вычислительной техники, а именно - к устройствам преобразования, информации для . UBN и может применяться для параллельного преобразования нескольких частотноимпульсных сигналов при последовательном вводе кодов в вычислительное устройство.

Известен преобразователь сигналов в цифровой код, содержащий формирователь временного интервала, соединенный с вход- то ной схемой совпадения, включенной на входе накопительного счетчика„собирательные схемы и формирователи импульсов j1$.

Известен также преобразователь часто- тб та-код, содержащий счетчик, регистр пере полнения, блоки управления, устройства сит хро-. ниэации и буферные регистры f2), Однако известные устройства сложны.

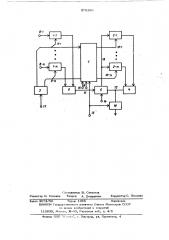

llewü изобретения — упростить преобраэо- Е ватель частота-к од, Это достигается тем, что многоканальный преобразователь "частота-код, содержащий .распределитель управляющих импульсов, элемент сборки и в каждом канале приемный и регистр и буферный регистр, подключенный управляющим входом к,соответствующему выходу распределителя управляющих импульсов и выходом к соответствующему входу элемента сборки, снабжен распределителем циклов обработки каналов и последователь но соединенными вторым элементом сборки, сумматором и блоком ключей передачи информации, причем выходы распределителя циклов обработки каналов подключены к соответствующим входам приемных регистров и к соответствующим входам распределителя управляющих импульсов, выходы приемных регистров соединены с соответствующими входами второго элемента сборки, второй выход сумматора подключен к вторым входам буферных регистров, а вход первого элемента сборки - к входу блока ключей передачи информации, второй вход которого соединен с тактовым входом распределителя управляющих импульсов, а выход — с выходом преобразователяя.

На чертеже показана принципиальная электрическая схема многоканального преобразователя.

57 0196

Предлагаемое устройство содержит приемные регистры 1-1 — 1-п, буферные регистры

2-1 - 2-п, распределигвль 3 циклов обраоогки каналов, элемент 4 сборки, с лмагор

5, второй элемент 6 сборки, распределитель 5

7 управляющих импульсов, входные цепи 8., ° 8-ц приема частотно-импульсных сигналов, управляющие цепи 9-1 - 9-tt.распределителя циклов, управляющие цепи 10-1 - 10-г распределителя управляющих импульсов, вы- 10 ходную цепь 1Ц второго элемента сборки, выходную цепь 12 элемента сборки, входную цепь 13 опроса устройства, тактовую цепь 14 сумматора, тактовую цепь 15 распределителя управляющих импульсов, адресную цепь 16 распределителя управляющих импульсов, входную цепь 17 распределителя циклов, выходную цепь 18 сумматора и блок 19 ключей передачи информации, Преобразователь работает слвдующи . 20 образом.

Часгогн импульсная энакопеременнеч информация поступает по цепям 8 1 - 8- на входы двухразрядиых приемных регистров

1-1-1-ц., причем в первом разряде фиксируется поступление входного импульс в каждоМ канале, а во втором - вго знак.

Опрос регистров $-.1-1- д осуществляет ся поспвдоватвж о во времени по сигналам в цепях 9 1-9- tj распределителя 3 циклов.

Содержимое одного иэ регистров 1=1-1-gпоступает через элемент 6 сборки, далее по цепи 11 на вход сумматора 5. Одновременно распределитель 7 в соогветствии с сиг налом в цепях 9-1- 9 ц;формирует в це1 35 пях 10-1-10= 6 сигнал опроса одиого иэ буферных регистров 2-2 - 2- %-. Содержимое одного из буферных регистров 2-2 - 2-й через элемент 4 сборки далее по цепи 12 поступает на второй вход с"ммагора, 5 и на информационный вход блока 19 ключей.

На выходной цепи 18.сумматора 5 в соответствии с тактовым сигналом в цепи

14 формируется результат сложения двух кодов: содержимого I буферного регистра и приемного регистра одноименных каналов пре образования.

Распределитель 7 в соответствии с такто вымя сигналами в цепи 15 осуществляет опрос, обнуление и запись информации в буферные регистры 2-1 - 2-г причем опрос и последующий сброс на 0 содержимого буферных регистров 2-1 — 2- а; одного из

55 каналов осуществляется либо в момент появления сигнала в одной иэ цепей 9=1«9= h. либо при поступлении и цепь 16 соогветсч вуюшего адреса канала. Результат перезаписывается в гог же предварительно обн» ленный буферный регистр 2 в соответствии с управляющим сигналом в цепях 10 1-10-Ь

При появлении в. цепи 16 адреса соответствующего канала преобразования распределитель 7 формирует в соответсгвуюшей цепи

10-1 - 10- rL импульс опроса соотвегсгвующего буферного регистра 2 -1-2-й, а при поступлении сигнала в цепь опроса 13 осуществляется передачи кода через блок 19 ключей на выход преобразователя.

Формула изобретения

Многоканальный преобразователь час»гота-код, содержащий распределитель управляющих импульсов, элемент сборки и в каждо, дом канале приемный регистр и буферный регистр, подключенный управляющим входом к соответствующему выходу распределителя управляющих импульсов, а выходом к соог» ввтсгвующему входу. элемента сборки, о тл и ч а ю шийся тем, что, с целью упрощения, он снабжен распределителем циклов обработки каналов и последовательно соединеннымн вторым элементов сборки, сум» магором и блоком ключей передачи информации, причем выходы распределителя циклов обработки каналов подключены к соответствующим входам приемных регистров и к соответствующим входам распределителя управляющих импульсов, выходы приемных регистров соединены с соответствуюшимщ входами второго элемента сборки, второй вы ход сумматора подключен к вторым входам буферных регистров, а вход первого элемента сборки — к входу блока ключей передачи информации, второй вход которого соединен с тактовым входом распределителя управляющих импульсов; а выход - с выходом преоб разова геля.

Источники информации, принятые во внима нне при экспергиэе:

1. Авторское свидетельство СССР

l4 443479, кл. Н 03 К 13/00, 1973.

2, Авторское свидетельство СССР

¹ 312379> кл. Н 03 К 13/00, 1973.

570196

Составитель В. Степанов

Редактор О. Стенина Техред A. Демьянова

К орректор С. Ямалова

Филиал ИПП "П:и «нт, г. Ужгород, ул. Проектная, 4

Заказ 3073/50 Тираж 1065 П одписное

0НИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5