Устройство преобразования однофазового логического сигнала в парафазный ток

Иллюстрации

Показать всеРеферат

Союз Сьветскик

Социалистических

Республик (61) Дополнительное к авт. свид-ву (22) Заявлено23.04.76 (21) 2353523/21

r. присоединением заявки № (23) Приоритет (43) Опубликовано 25.08.77.Бюллетень № 31 (46) Дата опубликования описания 27.09.77 (51) M. Кл

1I .)3 li 1<, л

Гасударственный комитет

Совета Министров СССР иа динам изобретений и аткрытнй (53) УДК 681.32.-1.;, ; (088.8) (72) Авторы изобретения

В. Е. Ашурков, В. Г. Гусев и М. b. Кравцов (71) Заявитель (54) УСТРОЙСТВО ПРЕОБРАЗОВАНИЯ

ОДНОФАЗНОГО ЛОГИЧЕСКОГО СИГНАЛА

В ПАРАФАЗНЫЙ ТОК

1 2

Изобретение относится к импульсной гехнике.

Известно устройство для преобразования логических сигнялов, состоящее из парафазного передатчика, работающего m напряжений уровней T àíýmñãîðíorðàíçècòîðíûõ логических схем (ТТЛ) и диодно-транзисторных логических схем (ДТЛ), и имеющее на вьзсоде ло.и -еские ключи, которые возбуждают двухпроводную линию связи. Прием сигнала то с атой линии осуществляется компаратором.

Однако в атом устройстве преобразование однофазного сигнала в паряфазный осуществляется путем включения дополнительного иьзертирующего каскада, что приводит к15 к увеличению задержки одного из фронтов сигнала относительно другого и может сформировать ложнь|й сигнал на выходе компаратора.

Наиболее близким к предлагаемому являет- рц ся устройство, содержащее логический алеM« 2È-ИЛИ, состоящий из двух входных многоамиттерных транзисторов, базы которых через резисторы соединены с источником питания, а коллекторы соединены с базами 25 выходных транзисторов, коллекторы когорых через резисторы соединены с источником питания, а амиттеры соединены между собой и через токсзадающий резистор подключень. к источнику питания, причем один амиттер первого многоачиттерного транзистора подключен к первому источнику входного сигнала, два других амиттера соединены между собой, с тремя амигтерами второго многоамиттерного транзистора и со вторым иоточником входного сигнала.

Целью изобретения является повышение быстродействия и почехоусгойчивости.

Это достигается тем, что в угтройство, содержащее логический элемент 2И-ИЛИ, состоящий из двух входных многоамитгерных транзисторов, базы которых через резисторы соединены с истсчником пигания, я коллекторы соединены с базами выходных транзисторов, коллекторы которых через резисторы соединены с источником питания, а амигтеры соединены между собой и через токозадаюший резистор подключены к источнику питания, причем один ачиттер первого многоа лиггерного транзистора

5) 7 (!2 С1 1. подключен )! НН1)вэл)у источнику вхс)днэг0 сигналя, двл других эмиттера сэедн»ены между собой, с 1ремя эмиттерлми втэрог0 мнэгоэмиттер))эгэ rpBH"))Icr01))1 H сi) втор);IM истэчникОм вхОднэго сигналар введен диОД 5 и дополнительный трлн зис тор, база к этэр эгo соединена с эмиттеэами Выходных транзисторов логического элемента 2И-ИЛИ, эмиттер которого соединен с источником питания, а коллектор соединен с четвертым 1О змиттером второго многоэмиттерного транзистора непосредственно и через диод с чет вертым эмиттером первого многоэмиттерного транзистэра.

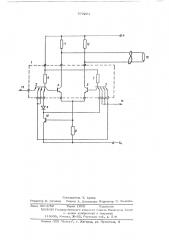

На чертеже приведена принципиальная !5 злек трическая схема предлагаем Ого устр ойс тва, Устройство содержит логический элемент

2И-ИЛИ 1, состоящий из многоэмиттерных транзисторов 2 и 3, Одноэмиттерных тран- 20 зисторов 4 и 5 и резисторов,6 и 7, токозядающий резистор 8, диод 9, дополнительный транзистор 1О, резисторы 11 и 12.

HG ВхОды 13 и 14 подаются вхОдные сигналы, 15 - нагрузка. 25

Устройство работает следующим образом.

Если на входы 13 и 14 пода ь сигналы, уровни которых соответству!От логической

1", то через резистор 6 течет тэк, насыщающий переход база-коллектор транзистора ЗО 2 и базовый переход транзистора 4. При этом и через резистор 11 течет выхэдной коллекторный ток и ток цепи змиттера транзистора 4, который создает падение напряжения на резисторе 8. Приувепичениинапряжения на резисторе 8, величины превышающей пороговое напряжение перехода база-эмиттер транзистора 10, в его коллекторной цепи, в цепях диода 9 и эмиттера транзистора 2 появляется ток, который снижает базовый ток транзистора 4. В результате этого кол«лектэрнь!й ток транзистора 4 фиксируется на уровне с)бэ ° !) т

R 15 где Л» - то!с коллектора;

0I) - напряжение база-эмиттер;

Р— величина резистора; фт - фиксирующий ток, и весьма незначительно завис!ст от величины напряжения питания и сопротивления нагрузки, При етом транзистор 5 закрыт, так как электрический потенциал на его базе ниже потенциала базы транзистора 3 на величину падения напряжения на открытом диоде 9, При подаче логического сигнала уровнем равным О ня вход 13 через резистор 6, ))01)ехoII б!)Ол-эл)))тт01» р!))! ЗнстОра 2 ))()эт! кает ток> llлсы))(ак)!)))!и вход))эй т1)/))!.)исто!) 2, Korэ1)Еэ)1! Зя )ТН1)ле т т1)лис)ис тэ1) 4 и диОд 9) )! э в э10)I случае эткрь)влется трлнзистос) 3, фиксация Kэ )))эктор))эгэ тэка котэрогэ определяет ся лналэгично, уклзаннэл)у вьпце.

При подл )О )га вход 14 сигналя, соответствующего логическому "О", транзисторы 2 и 3 закрыты незлвисимо от наличия сигналов на входе 13.

В связи с тем чтО транзнстОр6! 4 и 5 работают так источник тока, их режимы не зависят or изменения электрического потенциала коллекторов в широких пределах, в результате чего синфазная помеха, значительно превышающая выходное напряжение, не искажает информацию, а сочетание дифференциальной схемы включения транзисторов 4 и 5 с ненасыщенным режимэм работы и небольшим количеством актиьных элементсв обеспечивает минимальное время задержки сигнала.

Формула изобрете ння

Устройство преобразователя однэфазного логического сигнала в парафязный ток, ссдержащее логический элемент 2И-ИЛИ, состоящий из двух входе!ых многоэл)итте() ных транзисторов, базы которых через резистэры соединены с первой шиной источншсом питания, а коллекторы соединены с базами выходных транзистэров, коллекторы которых через резисторы соединены с первойй шиной источника питания, а эми тте ры соединены между собой и через тэкозадаю)ций резистор подключены к второй шине источника питания, причем один эмиттер первого многоэмиттерного транзистора подключен к первому источнику входного сигнала, два других эмиттера соединены между собой, с тремя эмиттерами второго многоэмиттерн) го транзистора и со вторым источником входного сигнала, о т л и ч а .о щ е е с я тем, что„с целью повышения быстродействия и помехоустойчивости, в него введен диод и дополнительный транзистор, база которог0 соединена с амиттерами выходных

rpa!1a»cropoa логического элемента 2И-ИЛИ, эмиттер-c aropo!I шиной источника питания, а коллектор — с )етве!)тыл! эммитером второго из упомянутых многозммитерных транзисторов непосредственно и через диод — с четвертым эммитером первого многоэммитерного транзистора.

13 0201

Составитель Т. Артюх

Редактор О. Стенина Техред А. Демьянова Корректор C.

Заказ 3073/50 Тираж 1065 П оддисн ое

ИН1И1ПИ Государственного комитета Совета Министров СССР и 1 делам изобретений и открытий

113535, Москва, Ж-35, Рвуисквв ввб., в. 5У4

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4