Устройство для передачи цифровых многоканальных сообщений

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Ресяубпик

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

k АВТОРСКОМУ СВИДЕТИЛЬСТВУ (i)) 87О207 (6!) Дополнительное к авт. свид-ву(22) Заявлено 16.12.75(21) 2199773/09 с присоединением заявки №вЂ” (23) Приоритет— (5l) М. Кл.

Н 04 Ю 6/00

Государственный комитет

Совета Министров СССР

Ilo делам изобретений и открытий (43) Опубликовано25.08.77.Бюллетень № 31 (53) УДК 62l.391. .3 (088.8) (45) Дата опубликования описания 11.10,77 (72) Авторы изобретения

B. E. Быков.и B. И. Грубов (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ЦИФРОВЫХ

МНОГОКАНАЛЪНЫХ i СООБШЕН ИЙ I

Изобретение относится к передаче информации и может использоваться в адаптивных многоканальных цифровых телеметрических системах для помехоустойчивости передачи сообщений с малой избыточностью.

Известно устройство для передачи цифровых многоканальных сообщений, содержащее

11 синхронизатор, аналого-цифровой преобразователь, элемент равнозначности, генераторы

М-последовательностей, блоки элементов И <0 и элемент ИЛИ $1) .

Однако в известном устройстве снижается помехоустойчивость передачи сообщений при сокрашении избыточности исходного сигнала. 15

Цель .изобретения — повышение помехоустойчивости передачи при сокрмцении избыточности исходного сигнала.

Для этого в устройство для передачи циф-20

poBblx многоканальных сообщений, содержащее синхронизатор, аналого-цифровой преобразователь, элемент равнозначности, генераторы Мпоследовательностей, блоки элементов И и элемент ИЛИ, введены коммутатор и анали-.

2 ,затор каналов, блок памяти, преобразователь параллельного - кода в последовательный,, старт-стопный,запоминающий блок, элемент задержки и последовательно соединенные счетчик и дешифратор. Выход коммутатора каналов подключен к входу аналот оцифрового преобразователя, выходы которого подключены к входам анализатора каналов непосредственно и через блок памяти, а через последовательно соединенные первый блок элементов И и преобразователь;параллельного кода в последовательный - к вхо:ду элемента равнозначности. При этом вйход анализатора каналов подключен к дру гим входам первого блока элементов И и через элемент задержки к входам второго блока элементов И. Его входы соединены с выходами дешифратора, а выходы второго блока элементов И подключены через соответствующие генераторы М-последовательностеи к входам элемента ИЛИ, выход которого подключен к другому входу элемента равнозначности, выход которого подключен к входу старт-стопного запоМинаюшего блока, второй вход которого соединен с вы570207

3 ходом другого генератора M-последовательности, управпяюший вход которэгэ и управпяюшие входы коммутатора каналов, блэка памяти и счетчика соединены с соответству. юшими выходами синхронизач ора.

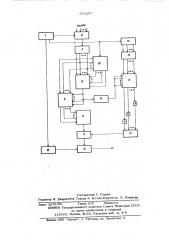

Не чертеже изображена структурная электрическая схема предлагаемого устройс ве.

Оно содержит синхронизатор 1, аналогоцифровой преэоразователь 2, элемент равнозначности 3, генераторь1. М вЂ” последовательностей 4, блоки элементов И 5,6 и элемент ИЛИ 7, коммутатор 8, анализатор

9 каналов, блэк памяти 10, преобразователь паралпельногэ кода B последовательный 11, старт-стопный зацоминеюший блок, 1 2, элемент задержки 13 и пэспедовательно соединенные счетчик 14 и дешифратор 15, причем выход коммутатора 8 каналов подключен к входу аналого-цифрового преобразоватепя 2, выходы круторого подключены к входам анализатора 9 каналов непосредственно и через блок памяти 10, а через последовательно соединенные первый блок элементов И 5, и преобразователь параллельного кода в последовательный 11 - к входу элемента равнозначности 3. Выход анализатора

9 каналов подключен к другим входам первого блоке элементов И 5, и через элемент задержки 13 к вхэдам второго блока элементов И 6, другие входы которого соединены с выходами дешифратора 15, а выходы второго блока элементов И 6 подключены через соответству|ошие генераторы М-последовательностей 4 к входам элемента ИЛИ 7, выход которого подключен к другому входу элементе равнозначности 3, выход котэрогэ подключен к входу стартстопного запомйнаюшегэ блока 12, второй вход которого соединен с выходом другого генератора Мпоследовательности 16, Его управпяюший вход и управляющие входы кэммутатора каналов

8, блока памяти 10 и счетчика 14 соединены с соответствующими выходами синхронизатора 1.

Устройство работает следующим образом

Сигналы сии:ронизаторе 1 управляют работой коммутатора 8 каналов с помощью которого на вход аналого-цифровэго цреобразователя 2 поочередно поступают сигналы всех Й канадов, а в счетчже 14 будет фик сироваться двоичный адрес текущего канала. Аналого-цифровой преобразователь 2 в соответствии с амплитудой входного сигнала вырабатывает кодовую комбинацию в виде параллельного двоичногэ кода. Разряды кодовых комбинаций по соответствуюшим шинам подаются на входы анализатора - каналов и блока памяти 10. С его выхода снимается кодовая комбинация в параллель нэм коде, отображающая значение сигнала данногэ KBHBfIB B точке отсчета, предшествующей рассматриваемой и этстэяшей на время, Pß авное периоду опроса. Входная и выходная кодовые комбинации сравниваются в анализаторе 9 каналов. Если абсолютная величина разности их значений меньше заданной величины, То на выходе анализатора 9 каналов сигнал отсутствует,при этом блоки элементов И 5 и 6 будут закрыты по управляюО шим входам. Вследствие этого разряды ийформациэнной кодовой комбинации на входы преобразователя параллельного кода в последовательный 11 не поступают. По этэй же причине не может поступить запускаюший

5 сигнал с выхода данногэ канале дешифратора 15 на вход сэответствуюшегэ генератора М-последовательности 4. Если указан-ная разность превышает по асбэлк.тнэй величине заданную, то на выходе анализатора каналов 9 образуется управляюший сигнал, который открывает первый блок элементов И 5, и текушая кодовая комбинация поступает на вход преобразэвателя параллельного„ кода в последовательный 1 1. Этот же управляюший сигнал с выхода анализаторе 9 каналов, задержанный элементом задержки

13 не время преобразования параллельного кода в:*последовательный, поступает на вхэды второго блока элементов И 6, и заЮ пускающий сигнал данного канала с соответствующего выхода дешифретора 15 подается для запуска генератора М-последовательности 4 денного канала, который вырабатывает циклическую М-последовательность, дпительность которой равна длительности одного символа (О" или «1") информационной двоичной комбинации, а количество циклов равно числу разрядов информационной двоичной комбинации.

40 Таким оразом, на входы элемента равнозначности 3 одновременно подаются один двоичный разряд информационной комбинации с выхода преобразователя параллельного кода в последовательный 1 1 и М-последовательность с выхода элемента ИЛИ 7 структуры, присущей только номеру данного ка: нала. На выходе элемента равнэзначности 3 будут последовательно сформированы Мпоследовательности структуры данного номе9 ра канала, промодулированные информационной двойчной кодовой комбинацией также данного канала (символу 1 . соответствует прямая М-последовательность, а-символу О"обратная). Аналогичным образом в предлагаемом устройстве будут сформированы Mпоследовательности структур, соответствующих номерам каналов, пэ которым текущие информационные кодовые комбинации являют ся сушественными (неизбыточными). Старт стопный запоминаюший блок 12 обеспечи570207

5 вает сдвиг М-последовательностей неизб ыточных каналов к началу кадра передачи инфор .мации за счет свободньг< канальных интервалоб с избыточными выборками и равномерную выдачу сообщений в канал связи. В 5 старт-стопный запоминающий блок 12 с выхода другого генератора М-последовательности 16 (маркера кадра) периодически с частотой опроса каналов поступает синхронизируюшая последовательность, которая пере-10 дается в начале каждого кадра и испольI зуется на приемной стороне для синхронйзации местного хронизатора.

Формула изобретения

Устройство для передачи цифровых мно-! гоканальных сообщений, содержащее синхронизатор, аналогб-цифровой преобразователь элемент равнозначности, генераторы Мпоследовательностей, блоки элементов И и элемент(ИЛИ, о т л и ч а ю m е е с я тем, что, с целью повышении помехоустойчивости передачи при сокращении избыточности исходного сигнала, введены коммутатор каналов, анализатор каналов, блок па- р мяти, преобразователь,параллельногокодав последовательный, старт-стоцный запоминающий блок, элемент задержки и последовательно соединенные счетчик и дешифратор, причем выход коммутатора каналов подключен к входу аналог -цифрового преобразоватв3Фя, выходы которого подключены к входам анализатора каналов непосредственно и через блок памяти, а через последовательно соединенные первый блок элементов И и преобразователь параллельного кода в последовательный — к входу элемента равнозначности, при этом выход анализатора каналов подключен к входам первого блока элемен|тов И и через элемент задержки — к вхоаам второго блока элементов И, другие входы которого соединены с выходами, дешифратсра„ a выходы второго блока элементов И подключены через соответствующие генера- торы М-последовательностей к входам элемента ИЛИ, выход которого подключен к другому входу элемента равнозначности, кыхоц которого подключен к входу стартстопного запоминающего блока, второй вход которого соединен с выходом цругс го генератора M-последовательности, управляющий вход которого и управлякяцие входы коммутатора каналов, блока памяти и счетчика соецинепы с соответствующими выходами синхронизатора.

1. Венедиктов М. Д. и др. Асинхронные адресные системы связи. М„Связь, 1968, с. 49-50.

570Z07

gó0äû

Составитель Г. Серова

Редактор H. Джарагетти Техред А. Вогдан,Корректор H. Ковалева

Заказ 3075/51! Тираж 81 5 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССРпо делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д, 4/5

Филиал ППП Патент, r. Ужгород, ул. Проектная, 4