Запоминающее устройство с перезаписью информации

Иллюстрации

Показать всеРеферат

О Il И С А Н И Е ((((579929

ИЗОБРЕТЕНИЯ

Союз Севетскитв

Социалистическим

Рес(тублик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 31.12.74 (21) 2090632/24 с присоединением заявки ¹ (23) Приоритет

Опубликовано 30.08.77. Бюллетень ¹ 32 (51) М. Кл G 11С 11/40

Государственный комитет

Савета Министров СССР ео делам иэебретвниа и открытий (53) УДК 681.327.66 (088.8) Дата опубликования описания 31.08.77 (72) Авторы изобретения

К, М. Кролевец и В. И. Невядомский (71) Заявитель (54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

С ПЕРЕЗАПИСЬЮ ИНФОРМАЦИИ

Изобретение относится к вычислительной и электронной технике, в частности к полупроводниковым интегральным запоминающим устройствам (ЗУ) .

Известны ЗУ с перезаписью информации, построенные как на основе запоминающих

МНОП-транзисторов (Ме — 5(зХ4 — SiOg — Si) (1), так и запоминающих МАОП-транзисторов (Ме — А1 0з — SiOg — Si) (2), содержащие накопитель и блоки управления, обеспечивающие перезапись и считывание информации.

Напряжение питания подключается в этих устройствах к нагрузочным шинам накопителя с помощью МНОП (МАОП)-транзисторов в диодном включении.

Недостаток названных устройств — низкая избирательность записи информации, связанная с неполной передачей напряжения питания на нагрузочные шины накопителя, вследствие потери порогового напряжения в МДП (МНОП, МАОП) -транзисторах при диодном включении.

Наиболее близким техническим решением к изобретению является ЗУ с перезаписью информации, содержащее накопитель, блок выборки столбцов и блок управления перезаписью; разрядные шины накопителя соединены с выходом блока выборки, а нагрузочные шины накопителя — с выходом блока управления перезаписью (3).

При приложении импульса записи к адресной шине няеопитслт! няпряжснl(с, 3lip21(l(ph ющес этот импульс в кана1ах певыбранных запомпнающпх МДП-транзисторов, подключенных затворами к адресной шине, меньше напР5(жепиЯ питанпЯ k(2 Bc, III IIII(1 IIOPQI Ового напряжен пя. 1 03T03(x H pl(2 ми, (итт де импу Ibся записп 00.(cc — - 35 В (! Напряжсн(ТН питаkIHkf il(cпее — — 24 В II_#_ccT MccTo (12p22HTHQQ и встраивание заряда, искажающее информациюпю в невыбранных транзистора.. накопителя, тяе кяе разность ямп1ит (ды пм1!уг(ься зяппсп и э(граниp IO(цcго напряжения пpcвышает гра— ничпое напряжение загшсп МДП-структуры.

15 В связи с этим амплитуда импульса записи в схемах большой информационной емкости не превышает — 30 В, (то приводит к низкому быстродействию в режиме записи информации.

20 Недостатки данного устройства состоят в малом быстродействии и низкой избирательности записи информации.

Цель изобретения — повышение быстродействия и пзбиратсльност записи информации.

Это достигается Icì, что I! устройство введены блоки запрета записи, вход каждого пз ео Горь(к сОединсп с соотвстс Иу!0(kj(I входо ( блока выборки столбцов. а выход подключен к нагрузочной шипе накопителя данного

30 стол бца.

570920

15 0

При этом блок запрета записи содержит управляющий и нагрузочный МДП-транзисторы, МДП-транзистор запрета записи и конденсатор, причем затвор транзистора запрета записи подкл!О !ен K входу" Олока, исток — к шине нулевого потенциала, сток — к истоку нагрузочного транзистора, затвору управляющего транзистора и к первому выводу конденсатора, исток управляющего транзистора и второй вывод конденсатора подсоединены к выходу блока, а сток управляющего транзистора, сток и затвор нагрузочного транзистора — к шине питания.

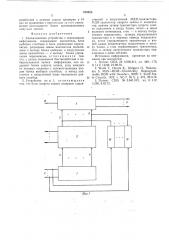

1-1а фиг. 1 представлена структурная схема запоминающего устройства с перезаписью информации.

Она содер>кит блок 1 выборки столбцов с входами 2, накопитель 3 с разрядными 4, адресными 5 и нагрузочными б шинами, блок

7 управления перезаписью с входом 8, шины

9 «Выход числа», блоки 10 запрета записи.

На фпг. 2 показана электрическая схема блока запрета записи. Она включает в себя управляющий МДП-транзистор 11, нагрузочный МДП-транзистор 12, МДП-транзистор 13 запрета записи, шину 14 импульсного питания, шину 15 постоянного питания, узловой конденсатор 16 столбца накопителя, конденсатор 17, узловой конденсатор 18 блока запрета записи.

Работает запоминающее устройство следующим образом.

Устройство переключается в режим стирания сигналом, подаваемым на вход 8 блока 7 управления перезаписью. Все запоминающие элементы накопителя 3 устанавливаются в состояние «О» при приложении напря кения стирания к адресным шинам 5 накопителя.

Для записи информации в ЗУ на вход 8 блока 7 управления перезаписью подается команда «Запись», к адресным шипам 5 накопителя прикладывается импульс записи, информация, поданная на входы 2 блока выборки, запоминается по выбранному адресу, При этом блоки 10 запрета записи в выбран«!ых столбцах накопителя обеспечивают разрешение записи «1», тогда как блоки запрета записи невыбранных столбцов коммутируют на нагрузочные шины 6 этих столбцов экранирующий потенциал, запрещая запись «1».

В ЗУ в режиме записи шина 14 отключается от источника импульсного питания и заземляется, на вход 8 подаются тактовые импульсы «1» с периодом, превышающим длительность отрицательных импульсов записи на величину длительности тактового импульса. Одновременно с импульсами записи, подключаемыми к выбранной адресной шине 5 накопителя 3, на входы блока выборки в двоичном коде поступает записываемое чис чо.

Если в столбец записывается «1», то транзистор 13 отпирается, на конденсаторе 18 устанавливается нулевой потенциал, транзистор

11 запирается и блок 10 запрета записи переводится в выключенное состояние. Узловой

65 конденсатор 16 после подачи на вход 8 тактового импульса разряжается до потенциа.!а «О».

Если на вход 2 блока выборки подано напряжение «О», то транзистор 13 заперт, кондснсатор 18 заряжен транзистором 12 до потенцна ia «1». В течение тактового импульса, подаваемого на вход 8, узловой конденсатор

16 разря«кается до потенциала «О», а конден".ÿToð 17 заряжается до потенциала «1» через нагрузочный транзистор 12, транзистор 11 отпирается. 11осле окончания тактового импульса подается импульс записи, конденсатор 16 заря«кается за время фронта нарастания импульса записи через транзистор 11 до напряжения постоянного питания за счет емкостной положительной обратной связи, обеспечивающей передачу нарастающего напряжения с истока транзистора 11 на его затвор в соответствии с соотношением емкостей конденсаторов 17 и 18 (максимальное значение емкости конденсатора 17 выбирается из условия

С!7) 4С!8) .

В режим считывания информации ЗУ переключается сигналом, подаваемым на вход 8 блока 7 управления перезаписью. Сигнал выбора столбца накопителя 3 поступает на вход

2 блока 1 выборки, с помощью разрядной шины 4 возбуждаются запоминающие элементы этого столбца, блок 10 запрета записи, соответствующий названному столбцу, выключается и не оказывает воздействия на нагрузочную шину 6. При последовательном приложен!!и к адресным шинам 5 накопителя напряжения считывания информация, записанная в запоминающих элементах выбранного столбца, по нагрузочной шине б передается на соответствующую шину 9 «Выход числа». В ЗУ в режиме считывания шина 14 подключается к источнику импульсного питания, на вход 8 б..!ока 7 управления перезаписью подается потенциал «О». Выбор столбца осуществляется подачей напряжения «1» на соответствующий вход блока выборки, транзистор 13 отпирается и соответствующий блок 10 запрета записи выключается.

Узловой конденсатор 16 заряжается до потенциала «1» в течение импульса питания по шине 14, после окончания которого к адресным шинам 5 накопителя прикладывается напряжение считывания, отпирающее только те запоминающие транзисторы, в которых записан «О». При этом узловой конденсатор 16 разряжается по нагрузочной шине 6 через открытый транзистор, по разрядной шине 4 на шину нулевого потенциала, и на шине 9 «Выход числа» устанавливается напряжение «О».

Считывание информации разрешено в промежуток времени, когда сигнал импульсного питания находится в состоянии «О».

Преимущества запоминающего устройства с перезаписью информации состоят в возможности увеличения информационной емкости до 4 Кб«!т в связи с повышением избирательности записи информации и повышения быст 570920 родействия в режиме записи примерно в 10 раз по сравнению с прототпгом а счет уменьшения длительности более высоковольтного импульса записи.

Формула изобретения

1. Запоминающее устройство с перезаписью информации, содержащее накопитель, блок выборки столбцов и блок управления перезаписью, разрядные шины накопителя подключены к выходу блока выборки, а нагрузочные шины накопителя — к выходу блока управления перезаписью, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия и избирательности записи информации, оно содержит блоки запрета записи, вход каждого из которых соединен с соответствующим входом блока выборки столбцов, а выход подключен к нагрузочной шине накопителя данного столбца, 2. Устройство по п. 1, отличающееся тем, что блок запрета записи содержит управляющий и нагрузочный МДП-транзисторы, МДП-транзистор запрета записи и конденсатор, причем затвор транзистора запрета записи подключен к входу блока, исток — к шине

5 нулевого потенциала, сток — к истоку нагрузочного транзистора, затвору управляющего транзистора и к первому выводу конденсатора, исток управляющего транзистора и второй вывод конденсатора подключены к выхо10 ду блока, а сток управляющего транзистора, сток и затвор нагрузочного транзистора подключены к шине питания.

Источники информации, принятые во внимание при экспертизе

15 1. Патент США № 3.508.211, кл. 340 — 173, G 11 С 1 1/40, 2.1.09.70.

2. Wada Т., Onoda К., Ishiguro Н., Nakanuma S. MAS — ROM — Е1ес1г1са11у Reprogrammable ROM with Decoder», IEEE Т. Solid Sta20 te Circuits, 1972, v. SC-7, № 5, р. 375, 29.3.72.

3. Патент США № 3.641.512, кл. G 1lC

11/00, 8.02.72.

570920

Фиг.2

Составитель В. Невядомский

Техред Е. Хмелева Корректор Л. Брахиииа

Редактор И. Грузова

Подписное

Типография, пр. Сапунова, 2

Заказ 1932(17 Изд. ¹ 697 Тираж 738 г1ПО Государственного комитета Совета Министров СССР по делам изобрстсний и открытий

113035, Москва, Ж-35, Рауьвская паб., д. 4/5