Арифметическое устройство

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Сеоэ Соаетснмя

Социалистических республик (11) 571808 (61) Дополнительное к авт. санд-ву(22) Заявлено 08.10.74(21) 2065360/24 с присоединением заявки №(23) Приоритет(43) Опубликовано 05.09.77.Бюллетень № 33 (4$) Дата опубликования описания 28.10.77 (51) М. Кл

G06 Г 7/S8

Геаударствеинай аоветет

Соеата Меаетрев СССР аа дилан азабратаааИ а аткрвютаИ (53) УДК 681.325 (088.8) (72) Авторы изобретения

Л. П. Горохов, Н. И. Манто, Д. К. Соловей н Г, Я. Шучинская (71) Заявитель (54} АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО

Изобретение относится к вычислительной технике и может найти применение в арифметических устройствах (АУ) ILBM последо нательного действия, имеюших систему команд, близкую к универсальной, н реализующих операцию вычитания модулей.

Известны АУ, в состав которых входит сумматор АУ, регистр операнда, дешифратор кодов операций, выполняюшие арифметические и логические операции над числами, после- 1а довательно поступаюшими на сумматор АУ

° ° представленными в дополнительном коде

1, 2). Однако АУ этих ЦВМ не реализует операции вычитания модулей, которые вынос ндотся в этих машинах программным спо )а собом, Ближайшим техническим решением к изобретению является АУ t 3), содержащее два сумматора, регистр операнда, дешифра тор кодов операции два элемента ИЛИ. Вы» 30 ход первого сумматора соединен с первыми входамн регистра операнда н второго сумма» тора, выход которого соединен с первым вхс дом первого элемента ИЛИ. Второй вход этого элемента соединен с первыми входа» 25

2 ми второго элемента ИЛИ, первого сумма тора и с выходом детнифратора "îäîâ опе раций вход которого соединен с первым входом устройства. Второй вход устройства соединен со вторым входом второго элемент» та ИЛИ. Второй и третий входы первого сумматора соответственно с выходами пер вого и второго элементов ИЛИ.

Недостатком этого устройства является длительное выцолнение операции вычитани» модулей.

Белью изобретения является повышение быстродействия АУ.

Эта цель достигается тем, что в предложенное АУ введен узел анализа знаков, первый вход которого соединен со вторым входом АУ, второй вход - с выходом ре гнстра операнда, третий вход с выходом дешифратора кодов операций, а выход - с третьими входами элементов ИЛИ, со вто» рым входом второго сумматора и четвер» тым входом первого сумматора.

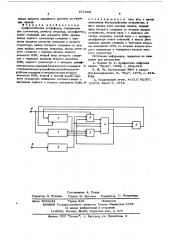

На чертеЖе представлена функциональная схема АУт последовательного действия.

571808 ода усз

Оно содержит регистр операнда 1, пер»

ый 2 и второй 3 элементы ИЛИ, первый

4 и второй 5 сумматоры, дешифратор кодов операций 6 и увел анализа знаков 7.

Входы регистра 1 соединены соответсз в венно с выходами сумматоров 4 и 5 вы» ход регистра 1 соединен со вторым входом узла анализа знаков и первым входом эле» мента ИЛИ 2.

Входы элемента ИЛИ 3 соединены со i0 вторым входом 8 АУ, а также с выходом дешифратора 6 и с выходом узла анализа знаков 7. Выход элемента ИЛИ 3 подключен i третьему входу сумматора 4. Ha.sxo ды элемента ИЛИ 2 подаются сигналы (кро- >5 ме выхода регистра 1) с выхода дешифрагде О - число, поступающее со вх ройствв;

b. - число из регистра 1. 35

На вход узла 7 поступают последоватеж но первое а и второе b число. Под воэ действием кода операции вычитания модулей (код ВМ) в узле 7 анализируются знаки исходных чисел. При положительных числах и вырабатываются сигналы ., ЭИ sign a = 0 и ВМ sign Ь 0 ., при жрипвтельных чис лах - сигналы ВМ signa = фйЦМ sign b = Я.В зависимости от выработанных узлом 7 car палов элементы ИЛИ 2 и 3 пропускают на 45 вход сумматора 4 исходный код первого числа а если выработан сигнал ВМ sign а =,О, инвертированный код первого числа а если выработан сигнал ВМ sign a--0, 50 исходный код второго числа b, если выработан сигнал ВИ sign Ь 0, инвертированный код второго числа b если выработан сигнал ВМ.sign Ь О, Поскольку АУ работает в дополнительном 55 коде то для выполнения операции вычитания числа должны быть преобразованы в код, дополнительный к исходнсму. Для атого к проинвертироввнному коду в момент сложения младших разрядов дотокна быт прибвэ- 60 тора 6 и узла анализа знаков 7. Выход элемента ИЛИ 2 соединен со вторым вхо дом сумматора 4. На первый и четвертый входы сумматора 4 подаются соответственно сигналы с выходов дешифратора 6 и узла анализа знаков 7. Выход сумматора 4 сое динан с первым входом сумматора 5. На второй вход сумматора 5 подключен выход узла анализа знаков 7. Вход дешифратора

6 соединен с первым входом 8 АУ. Входы узла анализа знаков 7 соединены с входом

8 АУ, выходами регистра 1 и дешифрвтора 6.

Узел анализа знаков 7 анализирует знаки исходных чисел, участвующих в операции.

Работа узла 7 иллюстрируется таблицей. лена +1, Прибавление +1. производится в сумматоре 4 под воздействием сигнала

НМ Ь{ пЬ=О (т. е. при b > 0), или (и) в сумматоре 5 под воздейсивием сигнала

ВИ signa=O (т. е.,:при И< 0).

Операция вычитания модулей выполняет ся эа два рабочих цикла. В первом цикле вЫчислений анализируются знаки исходных чисел. Во втором цикле вычислений в за» висимости от сочетания знаков выполняется собственно операция сложения или вычитания, результат которой и .представляет собой разность модулей исходных чисел.

Ускорение выполнения операции вычитания модулей достигается за счет того, что вместо нахождения модулей исходных чисел и йск: ледуюшего вычитания модуля вычитаемого иэ модуля уменьшвемого, нв что затрачивается пять рабочих циклов, производится анализ знаков исходных чисел, и в зависимости от их значений выполняется операция сложении или вычитания над исходными чи лами.

Таким образом, техник -акономический аффект изобретения состоит в ускорении времени выполнения операции вычитания модулей в 2,5 рвзв, что существенно снижает

571808

Составитель А. Уткин

Редактор Л. Утехина Техред О. Луговая Корректор С Патрушева

Заказ 3034/34 Тираж 818 Подписное

ЫНИИПИ Государственного комитета Совета Министров СССР по делам изобретений н открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, r. Ужгород, ул. Проектная, 4 общие затраты машинного времени на решэ иие задачи, Формула изобретении

Арифметическое, устройство, содержащее два сумматора, регистр операнда, дешифратор к кодов операций, два элемента ИЛИ, причем выход первого сумматора соединен с первыми входами регистра операнда н второго сумматора, выход которого соединен со втоI — с рым входом регистра операнда, выход котся 10 рого соединен с первым входом первого элемента ИЛИ, второй вход которого соединен с первыми входами второго элемента

ИЛИ, первого сумматора и с выходом дэшиф раторакодов операций, вход которого соединен 15 с первым входом устройства, второй вход ycr юйства соединен со вторым входом второго элемента ИЛИ, второй и третий входь йер" вого сумматора соединены соответственно с выходами первого и второго элементов ИЛИ, 20 о т л и ч а ю щ е е с и тем, что, с целью повышении быстродействия устройства, в чего введен узел анализа знаков, первый вход которого соединен со вторым входом устройства, второй вход - с выходом рэ гистра операнда, третий вход - с вилком дешифратора кодов операций, а выход арпа анализа знакоВ соединен с третьими входа» ми элементов ИЛИ, со вторым входом вто рого сумматора и четвертым входом первого сумматора..

Источники информации, принятые во вни мание при экспертизе:

1. Карцев И. А. Арифметика цифровых машин. Наука", 1969, с. 294 312.

2. Я. Чу. Организация ЭВМ и микро программирование. М. Мир", 1975, с 223

244.

3. Технический отчет. А 15.0 Я3.057.

052ТО. Книга 5, 1973.