Аналоговое запоминающее устройство

Иллюстрации

Показать всеРеферат

Союз Соеетскмв

Социалмстммескик

Республик

О П И С А Н И Е 5т н3

ИЗОБРЕТЕН Ия

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Йополвитетьное к авт. свид-ву (22) Заявлено 15.08,75 (21) 2163983/24 с присоелинеиием заявки №вЂ” (23) Приоритет (43) Опубликовано 05.09.77. Бюллетень №33 (45) Дата опубликования описания 31.10.77 (53) М. Кл 611С 27/00

Государственный аомвтет

Совета Министров СССР по делам изобретений и открытий (ЬЗ) УДК 681 327 66 (088,8) (72) Авторы изобретения

B. H. Мышляев, А, Г. Алексеенко и Е. A. Коломбет (71) Заявитель (54) АНАЛОГОВОЕ ЗАПОМИНАЮ?цЕЕ УСТРОЙСТВО

20

Изобретение относится к области вычислительной техники и может быть использовано в аналогоBhlx и аналого-цифровых вычислительных машинах и устройствах контрольно-измерительной техники.

Известно аналоговое запоминающее устройство, содержащее операционные усилители и ключи на

МОП-транзисторах, в которых применены импульсные методы регулировки ошибки (1) .

Однако в известном аналоговом запоминающем устройстве ошибка, обусловленная передачей управляющего сигнала с затвора на запоминающий конденсатор через внутреннюю емкость затвор- сток второго МОП-транзистора, изменяется изэза старения элементов, нзменейня температуры и напряжения питания и т.д,, поэтому такая ошибка не может быть полностью скомйенсирована за один цикл ручной подстройки. Кроме того, запоминающий конденсатор заряяается через два последовательно включенных МОП- транзистора, что увеличивает время выборки.

Наиболее близким по технической сущности является аналоговое запоминающее устройство (2), содержащее МОП-транзисторы, затворы первого н второго которых соединены с шиной управления.

Подложка н исток первого МОП-транзистора под. 2 ключены к шине, запирающего напряжения и входу устройства соответственно, Затвор третьего

МОП-транзистора соединен с шиной отпнрающего напряжения, истоком BTopofo МОП-транзистора и через опорный элемент с подложкой и со стоком второго МОП-транзис?ора я подложкой третьего

МОП-транзистора, сток которого соединен с одной нз обкладок конденсатора. Другая обкладка конденсатора подключена к шине нулевого потенциала.

Недостатком такого устройства является низкое быстродействие.

Целью изобретения является повышение быстродействия устройства.

Эта цель достигается тем, что в предложенное аналоговое запоминающее устройство введены операционные усилители, дополнительный конденсатор и дополнительные МОП-транзисторы, затворы которых подключены к шиве управления. Подложки и стоки первого и второго дополнительных

МОП-транзисторов подсоединены к подложке и стоку первого МОП- транзистора соответственно.

Сток первого МОП-транзистора соединен с инвертирующим входом первого операционного усилителя, выход которого соединен с его инвертирующим входом и через третий МОП-транзистор с неинвер571832 тирующим входом второго операционного усилители, выход которого соединен с выходом устройства, с подложкой третьего МОП-транзистора, с истоком первого дополнительного МОП- транзистора и через последовательно соединенные третий, четвертый и пятый донолнительиые МОП-транзисторы с инвертирующим входом второго операционного усилителя и через шестой дополнительный

МОП-транзистор с шиной нулевого потенциала.

Подложка третьего дополнительного МОП-транзистора соединена с шиной запирающего напряжения, исток второго дополнительного МОП-траизистора— с шиной нулевого потенциала, Подложки четвертого, пятого и шестого дополнительных МОП-транзисторов подключены к стоку четвертого и истоку пятого дополнительных МОП-транзисторов и к одной из обкладок второго конденсатора, другая обкладка которого соединена с шиной нулевого потенциала.

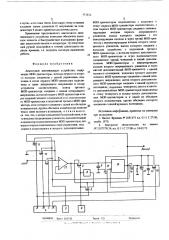

На чертеже представлена электрическая схема ус.грай ства.

Оно содержиг первый 1, второй 2 и третий 3

МОП-транзисторы, шину управления 4, шину запирающего напряже щя 5, шину отпирающего напряжения б, резистор 7, опорный элемент 8, первый и дополнительный конденсаторы 9 и 10, дополнительные первый 11, второй 12, третий 13, четвертый 14, пятый 15 и шестой 16 МОП-транзисторы и первый 17 и второй 18 операционные усилители.

Предложенное устройство работает следующим образом.

На и, вом этапе в режиме автоматической подстройки устройства, которая проводится периодически (например, через каждые 64 цикла выборки и хранения входного сигнала) на отвод I I I шины 4 управления поступает отпирающее напряже. ние (для диапазона входных сигналов 10 В прв использовании р-канальных МОП-транзисторов отпирающее напряжение выбрано равным примерно

-20 В, а запирающее — +10 В). При этом МОП-транзисторы 11, 13, 14 и 15 открьпы, а МОП-транзисторы 1, 3, 12 и 19 закрыты. Выходное напряжение усилителя 18 всегда равно разности напряжений на его входах, поэтому напряжение на затворе

МОП-транзистора 2 равно напряжению на его выходе минус падение напряжения на опорном элементе 8.

Поскольку падение напряжения на опорном элементе 8 больше порогового напряжения

МОП- транзистора 2, последний оказывается откры; тым и конденсатор 9 заряжается донапряжения,, равного выходному напряжению усилителя 17, т.е, до потенциала земли. Конденсатор 10 также заряжается до потенциала земли через открытые

МОП-транзисторы 14 и 15, На втором этапе в режиме автоматической подстройки напряжение на отводе 1I шины управления 4 становится отпирающим, поэтому отпирается

МОП-транзистор 3, напряжение на опорном элеменО,..... arnn .. ъ б

О

2(25

Ъ

4

При этом из-за пролезания сигнала с затвора

МОП-транзистора 2 через его внутренние емкости на конденсаторе 9 возникает и запоминается помеха, равная ошибке выборки. Величина этой помехи не зависит от уровня входного сигнала, но может медленно меняться со временем из-за старения элементов и изменения температуры и питающих напряжений. Конденсатор 10 также заряжается до напряжения, равного ошибке выборки через

MO1I-транзисторы 14 и 15, В конце второго этапа режима автоматической подстройки на отводах

1-I I I шины управления 4 устанавливается запирающее напряжение, а на обводе И вЂ” отпирающее напряжение, поэтому напряжение, равное ошибке выборки, запоминается на конденсаторе 10 и через открытый МОП-транзистор 16 попадает на первый вход усилителя 18. Теперь аналоговое запоминающее устройство готово к выборке и хранению входного сигнала. Емкость конденсатора 10 выбрана достаточно большой для того, чтобы ее разрядка не вносила заметной ошибки при выборке и хранении входного сигнала. Входное сопротивление усилителя 18 очень велико, а токи утечки транзисторов 13, 15 и 16 малы, так как напряжение между их подложками, входами и выходами не превосходит

0,2 — О,ЗВ. Благодаря этому и большой емкости конденсатора 10 напряжение ошибки выборки сохраняется на нем без заметных искажений в течение большого числа циклов выборки и хранения входного сигнала.

В режиме выборки на отводы и IV шины управления 4 поступают отпирающие напряжения, а на второй и третий запирающие, поэтому

МОП-транзисторы 1 и 16 открыты, Открыт также и

МОП-транзистор 2, как это рассматривалось выше, а все остальные МОП-транзисторы закрыты. При этом конденсатор 9 быстро заряжается через открытый МОП-транзистор 2 до уровня входного сигнала. В этом режиме увеличение (уменьшение) найряжения на входе МОП - транзистора 1 приводит к автоматическому увеличению (уменьшению) напряжения на затворе МОП-транзистора 2, так что разность между напряжениями с выхода МОП-транзистора 2 и его затвора остается постоянной независимо от уровня входного сигнала н примерно равной падению напряжения на опорном элементе 8, При переходе к режиму хранения напряжение на отводе 1 шины. управления 4 становится запирающим, а на отводе I I — отпирающим, На отводе И сохраняется запирающее напряжение@ а на отводе

IV отпирающее, поэтому отпираются МОП - тран. зисторы 3 и 12 и запираются МОП-транзисторы 1 и

2. При этом на конденсаторе 8 запоминается входной сигнал плюс напряжение, соответствующее ошибке выборки. Напряжение на выходе усилителя 18 равно разности напряжений на его входах, т.е. входному сигналу. На вход усилителя 17 через открытый МОП-транзистор 12 подается напряжение с выхода усилителя 18 и поэтому разность напряже571832 к нулю, а его токи малы. Благодаря этому и малым входным токам усилителя 18 напряжение на конденсаторе 9 может храниться достаточно долго.

Применение предложенного аналогового запоминающего устройства йозволяет обеспечить высокую точность и быстродействие выполнения функции аналоговой памяти в аппаратуре, не допускающей ручной подстройки в течение длительного периода времени, т.е. получить высокую надежность работы, 10

Формула изобретения

Аналоговое запоминающее устройство содержащее МОП- транзисторы, затворы первого и второго которых соединены с шиной управления, подложка и исток первого МОП-транзистора подключены к шине запирающего напряжения и входу устройства соответственно, затвор третьего сО

МОП-транзистора соединен с шиной оп7ирающего напряжения, истоком второго МОП-транзистора и через опорный элемент с подложкой и со стоком второго МОП-транзистора и подложкой третьего MOII-трап зистора, сток которого соединен с одной из обкладок конденсатора, другая обкладка конденсатора подключена к шине нулевого потенциала, о т л и ч а ю щ е еся тем, что, с целью повышения быстродействия, в не. го введены операционные усилители, дополнительный конденсатор и дополнительные МОП- транзисторы, затворы которых подключены к шине управления; подло1кки и стоки первого и второго дополнительных

МОП-транзисторов подсоединены с подложке и стоку первого МОП-транзистора соответственно, а сток первого МОП-транзистора соединен с неинвертирующим входом первого операционного усилителя, выход которого соединен с его инвертирующим входом и через третий МОП-транзистор слеинвертнрующим входом второго операционного усилителя, выход которого соединен с выходом устройства, с подложкой третьего

МОП-транзистора, с истоком первого дополнительного МОП-транзистора и через последовательно соединенные, третий, четвертый и пятый дополнительные МОП-транзисторы с инвертирующим входом второго операционного усилителя и через шестой дополнительный МОП-транзистор с шиной нулевого потенциала; подложка третьего дополнительного MOII-транзистора соединена с шиной запи. рающего напряжения; исток второго дополнительного МОП-транзистора соединен с шиной нулевого потенциала; подложки четвертого, пятого и шестого дополнительных МОП-транзисторов подключены к стоку четвертого и истоку пятого дополнительных МОП-транзисторов и к одной из обкладок второго конденсатора, другая обкладка которого соединена с шиной нулевого потенциала.

Источники информации, принятые во внимание при экспертизе:

1. Патент Франции М 2081675 кл. 6 11 С 27/00, опубл, 1970, 2. Авторское свидетельство по заявке . Х 2107579/24, кл. 6 11 С 27/00 от 24.02.75.

ЦНИИПИ Заказ 3Q37/35

Тираж 729

Подписное