Делитель частоты импульсов с переменным коэффициентом деления

Иллюстрации

Показать всеРеферат

Союз Советских

Соцмлнетнчаскна республик

Оп ИСАНИЕ

ИЗОБРЕТЕНИЯ

К аВТОРСКОМУ СВИДЙТВДЬСТВУ (61) Дополнительное к «вт. свид-ву0» 571911 (51) М. Кл.

Н 03 К 21/32 (22) ЗаявлЕно 12.05.76(2l) 2359974/21 е присоединением заявки И9 - . (23) Приоритет(43) Опублнковано05.09,77,Бюллетень М 33 (45) Дата. опубликования описания. 12.10. 77

Г99ударзт99иай ssrersr

Сзевтз И9999тр99 СССР

99 ДМАИм 9399Р9т9999 . а 9ткРыткЯ (53) УДК 621,374.31 (088.8) (72) Авторы изобретения

Д, Г, Нисневия н 8.. П. Гусев (71) Заявитель (54) ДЕЛИТЕЛЬ ЧАСТОТЫ ИМПУЛЬСОВ С ПЕРЕМЕННЫМ

КОЭФФИЦИЕНТОМ ДЕЛЕНИЯ

1 . Изобретение относится к импульсной технике, Известен делитель частоты импульсов с переменным коэффициентом деления, содержащий два счетчика, числа на которых умень- 5 шаю4ся в процессе счета, блок управления, состоящий из логических элементов, ряд переключателей, допускающих предварительную установку счетчиковт два вентиля, направляющие входной сигнал на соответствую- Io щий счетчик (1 .

Недостаток данного делителя заключается в его сложности.

Наиболее близким по технической сущнос- Iy ти и достигаемому результату к изобретению является делитель частоты, содержащий блок тактового питания один вход которого соединен с блоком управления, а другой с источником входного сигнала, а выходы соеди то иены со входамн управления двухтактового счетчика импульсов> выходы которого соедя иены с двумя входами блока управления, третий вход которого подключен к соответствующему выходу задающе> о блока (2).

Недостаток такого делителя заключается в недостаточном быстродействия.

Целью изобретения является повышение быстродействия.

Поставленная цель достигается тем, что

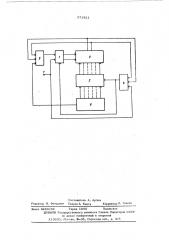

s д е л и т еeл ь b ч а ст о т rыr, содержащий блок тактового питания, один вход которого соединен с блоком управления, а другой - с источником входного сигнала, а выходы соединены со входами управления двухтактного счетчика импульсов, выходы которого соединены с двумя входами блока управления, третий вход которого подключен к соответствующему выходу задающего блока, введены блок памяти и триггер записи, причем входы блока памяти поразрядно подключены ко входам двухтактного счетчика импульсов, а вход управления блока памяти coegHHeH с выходом триггера записи и третьим входом блока тактового питания, при этом входы триггера записи соединены соответственно с выходами двухтактного счетчика и с источником входного сигнала, Структурная электрическая схема делителя приведена на чертеже.

; 571911

Делитель содержит блок тактового пита ния ., двухтактный счетчик импульсов 2, блок памяти 3, триггер записи 4, блок управления 5, задающий блок 6. б Входной сигнал подан на вход 7. Источники питания и вход входного сигнала на схеме не показаны.

Принцип работы делителя заключается в следующем. фО

В процессе работы устройства можно раэ1 личать цикл счета и цикл записи.

l. Рассмотрим деление на нечетный .коэффициент у " 5. цикл счета.

Триггер записи 4 находится в положении

"0 (или 1 ), запрещая считывание информации с блока Э, С задающего блока 6 идет сигнал "1", соответствующий нечетному коэффициенту деления. Блок управления на:20 ходится B положении "1" (или "О ), разрешая переключение блока 1 от сигнала У.

При этом осуществляется переключение счетчика 2 импульсов, B таком режиме де 3 литель работает до установки счетчика в (К - 1)-е положение, где g — емкость счетчика 2 импульсов. Установка его в (Ц - 1)-е положение происходит под воздействием (ц - 1)-го импульса каждого

30 цикла деления, цикл записи.

После установки счетчика 2 импульсов в положение (ht - 1) осуществляется переключение блока управления 5 в положение

О (или "1"). Тем самым запрещается

35 работа блока тактового питания 1 под воздействием сигнала Ц. „ . Наличие разрешающих сигналов является одним из условий для переключения триггера записи 4 s положение "1, вторым условием является окончание "д "-го импульса. После выполнения этих условий триггер записи 4 переключает ся в положение "l (или, 0 ), разрешая записать в счетчик 2 импульсов параллел ный код, соответствующий числу "й-.rl

После окончания записи указанного кода в счетчик 2 импульсов разрешающие сигналы пропадают. Тем самым снимается запрет работы блока тактового питания 1 .под воздействием сигналов U> а триггер записи

4 под врздействием (й + 1)-го входного импульса Ц устанавливается в положение

0 (или . ). Начинается новый цикл geления, аналогичный предыдущему.

Рассмотрим деление на четный коэффициент (ri * 4).

0икл счета, Триггер записи 4 находится в положении 0" (или "1"), запрещая считывание информации с блока 3. С задающего блока 6 идет сигнал (в данном случае "0 ), соотг ветствующий четному коэффициенту деления.

Благодаря этому блок управления все время работы с четным коэффициентом деления удерживается в положении, разрешающем переключение блока тактового питания 1 под т воздействием сигналов О, при этом осуих ществляется переключение счетчика 2 импульсов. 8 таком режиме делитель работает до установки счетчика в (Й - 1)-е положение.

l, )Цикл записи за исключением того, что блок управления 5 не переключается, происходит;аналогично циклу записи при нечетном коэффициенте деления, как описано выше, Повышение быстродействия достигается за счет сокращения величины задержки сиг нала в процессе перехода схемы от режима счета к режиму записи и обратно.

Формула изобретения

Делитель частоты импульсов с переменным коэффициентом деления, содержащий блок тактового питания, один вход которого соединен с блоком управления, другой,- с зажимом источника входного сигнала, а вы ходы соединены со входами управления двухтактного счетчика импульсов, выходы которого соединены с двуми входами блока управления, третий вход которого подключен к соответствующему выходу задающего блока, отличающийся тем, что, с целью повышении быстродействия, и него введены блок памяти и триггер., записи, причем вхо ды блока памяти поразрядно соединены с соответствующими выходами задающего блока, выходы блока памяти поразрядно подключены ко входам двухтактного счетчика импульсов, а вход управления блока памяти соединен с выходом триггера записи и треть им входом блока тактового питания, при этом входы триггера записи соединены соответственно с выходами двухтактного счег чика и с источником входного сигнала.

Источники информации, принятые во внимание при экспертизе:

1. Патент США М 3678398, кл. 32848 от 18.07.72 г.

2. Авторское свидетельство ¹ 434601 кл. Н 03 К 23/02 от 17.05.72 r.

571911

Составитель А, Артюх

Редактор В. Фельдман Техред 3. Фанта- Корректор И. Гокси

Заказ 3286/39 Тираж 1065 Подписное

БНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж36, Раушская наб., д. 4/5