Делитель частоты с дробным переменным коэффициентом деления

Иллюстрации

Показать всеРеферат

Союз Советскнх

Соцналнстнческнх

Реснублнк

ОПИСАНИЕ,в71в14

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СЬИДВТЕЛЬСТЬУ (61) Дополнительное к авт. свид-ву2 (й) М. Кл.

Н 03 K 23/02 (22) Заявлено 26,05.76pf) 2361712/21 с присоединением заявки №

Гасударстввннн|й наннтат

Саавта Мнннссраа СССР аа двлам нзаарвтвнчй н атнрытнй (23) Приоритет(53) 3 ДК 621.375. .3 (088.8)

1

1 " -"."-::: -в - - 1 — -.= I (43) Опубликоваио05.09.77 Бюллетень № ЗЗ (45) Дата опубликования описания 19.10,77 (72) Авторы изобретения

3. А. Бунщ, А. А. Вейде и Б. Н. Вейн (7!) Заяви тель (54) ДЕЛИТЕЛЬ ЧАСТОТЫ С ДРОБНЫМ ПЕРЕМЕННЫМ

КОЭФФИИИЕНТОМ ДЕЛЕНИЯ

Изобретение относится к импульсной технике.

Известен делитель частоты с переменным коэффициентом деления, содержащий декады с постоянными и переменными коэффициентами деления, трйггеры памяти и схемы И, который позволяет задавать коэффициент деления в виде десятичной дроби. Однако импульсы на выходе этого устройства распределяются неравномерно (1J.

l0

Наиболее близок к предлагаемому делитель частоты, содержаший декадный делитель частоты на целое число, входы установ. ки которого соединены с переключателем и первым выходом - С - триггера управле»- 15 ния, и сигнальный вход соединен с выходом логического элемента И, один вход которого связывается с источником входного сигнала, а другой - со вторым выходом С - триг» гера управления С, вход которого соединен ал с выходом декадного делителя частоты на целое число и входом декадного делителя частоты на дробное число, а К вход - с выходом логического элемента ИЛИ, один вход которого соединяется с источником я входного сигнала, и многовходовый логичеокий элемент И-ИЛИ-НЕ, первые входы логических элементов И которого соединены с переключателем дробных долей коэффициента деления 2).

Этот делитель недостаточно надежен.

Иель изобретения - повышение надежнос ти схемы — достигается тем, что в делитель частоты, содержащий декадный делитель час>тоты на целое число, входы установки которого соединены с переключателем и первым выходом RC - триггера управления, à ситiнальный вход соединен с выходом логического элемента И, один вход которого связывается .c источником входного сигнала, а другой соединен со вторым выходом RCтриггера управления. С-вход которого соединен с выходом декадного делителя частоты на целое число и входом декадного делителя частоты на дробное число, а К входс выходом логического элемента ИЛИ, один вход которого соединяется с источником входного сигнала, и многовходовый логический элемент И-ИЛИ-НЕ, первые входы логических элементов И которого соединены с

Э переключателем дробных долей коэффициента деленил, введены К RC-триггеров. и допоь.

: —.-::reëüíûé 9C - триггер управления, причем

„=ош М RC-триггеров соединены с вы ходам;; разрядов декадного челителя частоты 1 на дробное число, И входы всех N. RC-триг"ез:.. - с источником входного сигнала, вы» ходы поразрядно со вторыми входами элементов И многовходового логического элемента И-ИЛИ-НЕ; С вход дополнительного

RC - триггера управления соединен с источ ником входного сигнала, его R вход - с выходом многовходового логического алемента И-ИЛИ-НЕ, а выход - со вторым эхо дом логического элемента ИЛИ. 5

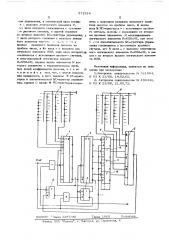

Структурная электрическая схема делителя.приведена на чертеже. делитель содержит декадный делитель частоты 1 на целое число, переключатель 2

КС-триггер управления 3, декадный дели- gp тель частоты 4 на дробное число, много входовый логический элемент И-ИЛИ-НЕ 5 переключатель дробных допей коаффициента деления 6, логический элемент И 7, логический элемент ИЛИ 8, RC-триггеры 25

9-12, дополнительный КС-триггер управления 13. делитель частоты с дробным перемен ным коаффициентом деления работает следу»» кяцим образом. Перед началом цикла деле- 30 ния s декадный делитель частоты 1 заносится число, являкяцееся дополнением целой части коаффициента деления до 10, триггеры 3, 9-12 и декады делители 4 устанавливаются в нулевое состояние, а 35 триггер 13 в единичное состояние (цепь установки на чертеже не показана).

Входные импульсы делителя проходят через элемент И 7 на декадный делитель частоты 1, где очи делятся на коэффициент, 40 равный целой части коаффициента деления. Сигнал с делителя 1 подается на первый вход триггера управления 3 и на делитель 4. Триггер 3 подает сигнал на вход синхронизации предустановки. делителя 1 и 45 вновь устанавливает в нем,коэффициент пересчета, равный целой части коаффициента деления. Одновременно нулевой сигнал с инверсного выхода триггера 3 блокирует элемент И 7. Делитель 4 переходит в первое состояние, т.е. на выходе первого разрядя появляется сигнал "единица, который переводит триггер 9 в единичное положение.

Лалее работа устройства зависит от коэффициента деления десятых долей.

Если переключатель 6 установлен в пер вые пять положений, на первом входе элемента И-ИЛИ-HE 5 имеется сигнал нуль, при изменении входного сигнала с единицы на нуль этот сигнал проходит через элемент

14

ИЛИ 8 на второй вход триггера управления

3 и возврашает его в исходное состояние, тем самым снимая блокировку алемента И

При этом декадный делитель частоты 1 делит количество импульсов на коаффициент, равный целой части коаффициента деления.

Если переключатель 6 установлен во вторые пять положений, на первый вход элемента И ИЛИ-HE 5 подается сигнал единица", сигнал с выхода изменяется с единицы на нуль и переводит триггер 13 в нулевое положение. При атом сигнал с инв сного выхода этого триггера через алел:ент

8 прикладывается ко второму входу триггера управления 3. При изменении входного сигнала с единицы на нуль он воэврашает триггер 9 в нулевое положение.

Следуюший входной сигнал устанавливает триггер 13 в единичное состояние, но пройти через элемент И 7 не может, так как триггер 3 находится в единичном состоянии, т.е. сигнал вычеркивается из входной импульсной последовательности, что аквивалентно Коэффициенту деления декадного дели теля на один больше, чем целая часть коэффициента деления. llaasure при изменении входного сигнала с единицы на нуль триггер управления 3 возврашается в исходное положение и т.д. Происходит цикл деления, в ко тором в зависимости от установки переключателя 6 из входной импульсной последовательности вы черкиваются соответствуюшие импульсы, чем обеспечивается получение заданного дробного коаффициента.

Йелитель частоты можно расширить как в сторону целых чисел коаффициента деления (при этом декадный делитель частоты 1 должен содержать столько декад, соединенных последовательно, сколько необходимо иметь десятичных знаков в целой части коэффициента деления), так и в сторону дробных знаков, подключая к выходу делителя десятых долей делители сотых долей и т.д., выходы разрядов которых через свой тритъгер должны подключаться Ко входам элемента И ИЛИ-HE 5.

В качестве триггеров 3, 9-13 могут быть применены D --триггеры, в которых на

)) вход подается сигнал единица, в качестве первого входа используется С вход, а в качестве второго - Й вход.

Ф ормула изобретения

Йелитель частоты с дробным переменным коэффициентом деления, содержаший пе» кадный делитель частоты на целое число, входы установки которого соединены с ïåðeключателем и первым выходом КСтриг

571914

Г(одннсное

Тираж 1065

Филиал (1Г1Г! Патент, r. Ужгород, ул. Проектная, ;- ра управления, а сигнальный вход соеди

:н с выходом логического элемента И, "".а,.н вход которого связывается с ™сточни;ем,входного сигнала, а другой соединен со вторым выходом RC-триггера управления, вход которого соединен с выходом декадного делителя частот.- :;. -.е.;о=. " ".:."о и входом декадного делителя частоты на дробное число, а М- вход - с выходом логического элемента ИЛИ, один вход которогоц) соединяется с источником входного сигнала, и многовходовый логичвскнн элемент.

И-ИЛИ-НЕ, первые входы элементов И которого соединены с переключателем дробных долей коэффициента деления, о т л и- (б ч а N ш и и с я тем, что, с целью повышения надежности, в него введены Й РСтриггеров и дополнительный С-триггер управления, причем С входы М РСтриггеровсоедн1(1(ИИГ1И Заказ 3287/40 нены с выходами разридов декадного делителя частоты на дробное число, К входы всех Nl ЙС-триггеров - с источником входного сигнала, выходы — поразрядно со вторыми входами элементов И многовходового логического элемента И-ИЛИ-НЕ, при этом

С ;-;од дополнительного RC-триггера управления соединяется с источником входного сигнала, его К вход - с выходом многовходного логического элемента И-ИЛИ-НЕ, а выход- со вторым входом логического элемента ИЛИ.

Источники информации, принятые во внимание при экспертизе:

1.Авторское свидетельство % 32 1964, Н 03 К 23/00, 14.02.65.

2. Авторское свидетельство Кя 436446, Н 03 К 23/00, 21.05.72