Управляемый интегратор

Иллюстрации

Показать всеРеферат

О П И С А Н И Е (и) 572794

ИЗОБРЕТЕНИЯ

Союз Савских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 02.06.75 (21) 2141622/21 с присоединением заявки М (23) Приоритет

Опубликовано 15.09.77. Бюллетень № 34

Дата опубликования описания 14.09.77 (51) М. Клз G 06G 7/18

Государственный комитет

Совета Министров СССР по делам изобретений (53) УДК 681 335.7 (088.8) и открытий (72) Автор изобретения

В. П. Иванов (71) Заявитель

ФОНД ЗХОНЕР1ба (54) УПРАВЛЯЕМЫЙ ИНТЕГРАТОР,1

Изобретение относится к устройствам измерительной техники, в частности к измерительным преобразователям аналоговых сигналов, Известен интегратор, содержащий управляемый ключ, транзисторы, резисторы, конденсаторы и диод (1).

Однако в данном устройстве управляемый ключ не обеспечивает прерывания процесса формирования напряжения на выходе генератора.

Известен управляемый интегратор, содержащий конденсатор, параллельно которому включен управляемый разрядный транзистор, зарядный транзистор, источник питания и резисторы (2).

Данное устройство также имеет отраниченные функциональные возможности.

С целью расширения функциональных возможностей интегратора в него введены управляемый ключ и источник смещения, одним полюсом подключенный к базе зарядного транзистора и к шине источника питания, другим полюсом — через управляемый ключ к эмиттеру зарядного транзистора, соединенному через резистор с входным зажимом устройства, а коллектор зарядного транзистора подключен к потенциальной обкладке конденсатора.

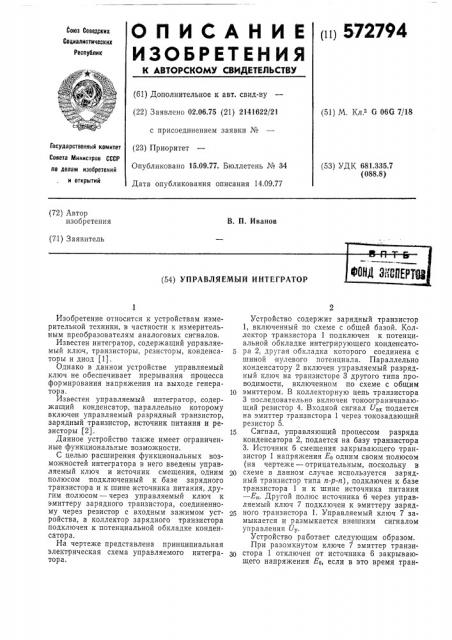

На чертеже представлена принципиальная электрическая схема управляемого интегратора.

Устройство содержит зарядный транзистор

1, включенный по схеме с общей базой. Коллектор транзистора 1 подключен к потенциальной обкладке интегрирующего конденсатора 2, другая обкладка которого соединена с шиной пулевого потенциала. Параллельно конденсатору 2 включен управляемый разрядный ключ на транзисторе 3 другого типа проводимости, включенном по схеме с общим

10 эмиттером. В коллекторную цепь транзистора

3 последовательно включен токоограничивающий резистор 4. Входной сигнал U» подается на эмиттер транзистора 1 через токозадающий резистор 5.

15 Сигнал, управляющий процессом разряда конденсатора 2, подается на базу транзистора

3. Источник 6 смещения закрывающего транзистор 1 напряжения Ес одним своим полюсом (на чертеже — отрицательным, поскольку в схеме в данном случае используется зарядный транзистор типа п-р-n), подключен к базе транзистора 1 и к шине источника питания — Ек. Другой полюс источника 6 через управляемый ключ 7 подключен к эмиттеру зарядного транзистора 1. Управляемый ключ 7 замыкается и размыкается внешним сигналом управления U .

Устройство работает следующим образом.

При разомкнутом ключе 7 эмиттер транзистора 1 отключен от источника 6 закрывающего напряжения Ео, если в это время тран572794

Формула изобретения

8six os у Π——

Составитель М, Аудринг

Техред И. Михайлова

Корректор О. Тюрина

Редактор Т. Янова

Заказ 1936/4 Изд. № 712 Тираж 818 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская на 6., д. 4/5

Типография, пр. Сапунова, 2

3 зистор 3 выключен сигналом Ур, то в схеме происходит процесс интегрирования сигнала

U», и конденсатор 2 заряжается от генератора тока, которым является транзистор 1, включенный по схеме с общей базой, причем величина зарядного тока определяется величиной входного напряжения U».

При замкнутом ключе 7 эмиттер транзистора 1 подключен к источнику б закрывающего напряжения Ео, при этом переход эмиттербаза транзистора 1 смещен в обратном направлении, при этом транзистор 1 закрыт, входной ток, задаваемый резистором 5, полностью переключен в источник б, и процесс интегрирования входного сигнала U„x принудительно прерывается на все время, пока ключ 7 остается замкнутым.

Таким образом, сигналом U, которым производится переключение ключа 7, осуществляется дьпдлнительное управление процессом интегрирования входного сигнала U».

Конденсатор 2 разряжается по завершении процесса интегрирования по сигналу Ур, включающему разрядный транзистор 3 (при этом входной сигнал U» должен либо полностью отсутствовать (U, 0), либо иметь обратную полярность, т. е. при разряде конденсатора 2 транзистор 1 должен быть закрыт. Если необходимо сбросить интегратор в исходное состояние при наличии на входе

4 напряжения U, рабочей полярности (U»+

ФО), то это может быть осуществлено одновременным замыканием ключа 7 и подачей сигнала Uz, включающего транзистор 3.

Управляемый интегратор, содержащий конденсатор, параллельно которому включен

10 управляемый разрядный транзистор, зарядный транзистор, источник питания и резисторы, отличающийся тем, что, с целью расширения функциональных возможностей, в него введены управляемый ключ и источник

15 смещения, одним полюсом подключенный к базе зарядного транзистора и к шине источника питания, другим полюсом — через управляемый ключ к эмиттеру зарядного транзистора, соединенному через резистор с вход20 ным зажимом устройства, а коллектор зарядного транзистора подключен к потенциальной обкладке конденсатора.

Источники информации, принятые во внимание при экспертизе

1. Дьяконов В. П. Лавинные транзисторы и их применение в импульсных устройствах. М., «Сов. Радио», 1973, р. 5 и 41, с. 177.

2. М. П. Степаненко, Основы теории транзисторов и транзисторных схем, М., 1973, 30 рис. 20 — 7, с. 547.