Импульсный логарифмический усилитель

Иллюстрации

Показать всеРеферат

О П И С А Н И Е 1п1 572803

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Соеетски11

Социалистических

Республик (61) Дополнительное к авт. свид-ву (22) Заявлено 14.11.75 (21) 2192848/24 с присоединением заявки № (23) Приоритет

Опубликовано 15.09.77. Бюллетень № 34

Дата опубликования описания 14.09.77 (51) М. Кл.а С 06G 7/24

Государственнсчй комитет

Совета Министров СССР (53) УДК 681.335(088.8) по делам изобретений и открытий (72) Авторы изобретения

Л, М. )Кавороиков, В. H. Лапенко и H. Н. Шишкевич (71) Заявитель

Московский институт электронной техник

ЯПТБ

ФОвВД ЗЛСП .Р 3 ОД (54) ИМПУЛЬСНЫЙ ЛОГАРИФМИЧЕСКИЙ УСИЛИТЕЛЬ

Изобретение относится к вычислительной технике и может быть использовано в устройствах первичной обработки информации для уменьшения динамического диапазона входных сигналов.

Известен логарифмический усилитель на усил ителях постоянного тока (1, 2). Однако известный усилитель требует много времени на восстановление чувствительности. Из известных устройств наиболее близким к изобретеншо по технической сущности является усилитель, содержащий последовательно соединенные усилители постоянного тока, выходы которы.; подключены ко входам сумматора (2). Он характеризуется недостаточным быстродействием.

Целью изобретения является повышение быстродействия. В описываемом усилителе это достигается тем, что в пего введены логический элемент ИЛИ, элемент задержками, ключ, блок управления и интегратор, вход которого через последовательно соединенные ключ и элемент задержки подключен к выходу последнего усилителя постоянного тока, соединенному через блок управления с управляющим входом ключа, выход интегратора подключен к первому входу логического элемента ИЛИ, второй вход которого связан с источником входного сигнала, а выход логического элемента ИЛИ подключен ко входу первого усилителя постоянного тока и к одному из входов сумматора.

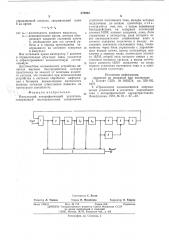

На чертеже показана блок-схема описываемого импульсного усилителя.

5 Он содержит логический элемент ИЛИ 1, последовательно включенные усилители постоянного тока 2, которые своими выходами соединены со входам и сумматора 3) выход которого является выходом всего устройства, 1р выход последнего усилителя постоянного тока соединен со входом элемента заержки 4 и со входом блока управления 5. Выходы элемента задержки 4 и блока управления 5 подключены соответственно к первому и вто15 рому входам ключа б, выход которого соединен со входом интегратора 7. Выход интегратора 7 соединен с первым входом логического элемента ИЛИ 1, второй вход которого является входом всего устройства, а выход соединен с первыAt усилителем постоянного тока.

Входной импульс через логический элемент ИЛИ 1 поступает на вход первого усилителя постоянного тока 2. Выходные импульсы усилителей 2 одновременно поступают на входы сумматора 3, на выходе которого реализуется логарифмическая характеристика.

С выхода последнего усилителя постоянного тока 2 импульс поступает на блок управлен ия 5, на выходе которого формируется

572803

Состаивтель С. Белан

Техред И. Михайлова

Корректор О. Тюрина

Редактор Л. Тюрина

Заказ 1936/11 Изд. Ко 712 Тираж 818 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и, опкрытий

113035, Москва, 7К-35, Раушская наб., д. 4/5

Типография, пр,. Сапунова, 2 управляющий импульс, закрывающий ключ

6 на время т HM+ tS где т — длительность входного импульса; т — дополнительное время, которое обеспечивает закрытое состояние ключа

6, необходимое для его лучшей работы и в период прохождения задержанного на элементе задержки

4 импульса.

Все остальное время интегратор 7 включен в отрицательную обратную связь усилителя и отфильтровывает низкочастотную составляющую.

Достоинством описываемого устройства является высокое быстродействие, которое практически, не зависит от величины входного сигнала, что позволяет при использовании устройства в системах обработки информации с большим динамическим диапазоном входных сигналов сущесгвенно повысить их пропускную способность.

-Формула изобретения

Импульсный логарифмичесиий усилитель, содержащий последовательно соединенные усилители постоянного тока, выходы которых подключены . ко входам сумматора, о т л ич а ю шийся тем, что, с целью повышения быстродействия, он содержит логический элемент ИЛИ, элемент задержки, ключ, блок управления и интегратор, вход которого через последовательно соединенные ключ и элемент задержки подключен к выходу последнего усилителя постоянного тока, соеди10 ненному через |блок управления с управляющим входом ключа, выход интегратора подключен к первому входу логического элемента ИЛИ, второй вход которого связан с источником входного сигнала, а выход логиче15 ского элемента ИЛИ,подключен ко входу первого усилителя постояннго тока и к одному из входов сумматора.

Источники информации, принятые во внимание при экспертизе

1, Патент США № 3662274, кл. 329-192, 1972.

2. «Применение насыщающихся операционных усилителей в усилителе переменного тока с логарифмической характеристикой».

Электроника, 1972, № 19, с. 27 — 30.