Устройство воспроизведения частоты входного сигнала

Иллюстрации

Показать всеРеферат

0Ц 572918

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (61) Дополнительное к авт. свид-ву (22) Заявлено 06.01.75 (21) 2092571/21 с присоединением заявки Ке (23) Приоритет

Опубликовано 15.09.77. Бюллетень Ке 34

Дата опубликования описания 13.09.77 (51) М. Кл. Н ОЗК ТЗ) 110

Государственный комитет

Совета Министров СССР (53) УДК 681.325(088.8) ло"делам изобретений и открытий (72) Авторы изобретения

В, Н. Семенов и В. 3. Лобанов (71) Заявитель (54) УСТРОЙСТВО ВОСПРОИЗВЕДЕНИЯ ЧАСТОТЫ

ВХОДНОГО СИГНАЛА

Изобретение относится к импульсной технике и может быть использовано в устройствах автоматического управления.

Известно устройство воспроизведения частоты, выполненное на базе управляемого делителя частоты и содержащее устройство ввода кода, выход которого подключен к входу запоминающего блока, выход которого соединен с установочным входом счетчика, на счетный вход которого поступает сигнал опорной частоты, причем выход счетчика подключен к входу селектора, выход которого соединен с входом установки нуля счетчика и с входом устройства ввода кода (1).

11едостатком устройства является значительная погрешность частоты воспроизводимого сигнала по отношению к частоте входного сигнала, в основном обусловленная относительной ошибкой запоминаемого числа за счет дискретности, так как это число за один период входного сигнала имеет малое значение при относительно невысоких значениях частоты опорного сигнала.

Целью изобретения является повышение точности воспроизведения частоты входного сигнала при относительно невысоких частотах опорного сигнала (до 1 МГц).

Это достигается тем, что в устройство воспроизведения входной частоты, содержащее запоминающий блок, выполненный в виде счетчика периодов опорной частоты, выходы всех разрядов которого через ключевые элементы подключены к установочным входам основного управляемого делителя частоты, и блок управления с двумя сигнальными входами опорной и входной частоты, и двумя управляющими входами, первый выход которого соединен с входом счетчика периодов опорной частоты, а второй и третий выходы подключены, соот10 ветственно, к управляющим входам ключевых элементов и к входу основного управляемого делителя частоты, введены ключевые элементы, дополнительный управляемый делитель частоты, счетчик периодов входного сигнала, делитель частоты, элементы И, ИЛИ и триггеры, при этом выходы старших разрядов счетчика периодов опорной частоты через дополнительные ключевые элементы подключены к установочным входам дополнительно упр ав20 ляемого делителя частоты, вход которого соединен с четвертым выходом блока управления, а выход подключен к первому входу первого элемента ИЛИ, к первому управляющему входу дополнительных ключевых элемен25 тов и входу делителя частоты, каждый из потенциальных выходов которого соединен с одним из входов соответствующих элементов И, другие входы которых подключены к потенциальным выходам счетного триггера, вход

30 которого соединен с выходом основного управ572918

55

65 ляемого делителя частоты и дополнительным управляющим входом ключевых элементов, причем выходы элементов И через второй элемент ИЛИ подключены к второму управляющему входу дополнительных ключевых элементов и к пятому выходу блока управления, шестой выход которого подключен к счетчику периодов входного сигнала, выходы всех разрядов которого через дешифратор нуля, формирователь и триггер подлючены к седьмому выходу блока управления, восьмой выход которого соединен со вторым входом первого элемента ИЛИ, выход которого подключен к девятому выходу блока управления.

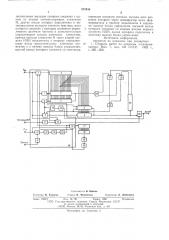

На черте>ке изобра>кена структурная электрическая схема предлагаемого устройства.

Устройство воспроизведения входной частоты содержит элемент И 1, установленный на входе счетчика 2 периодов опорной частоты, потенциальные выходы всех разрядов которого через ключевые элементы 3 установки кода подключены к установочным входам основного управляемого делителя 4 частоты, при этом выходы старших разрядов счетчика периодов опорной частоты через дополнительные ключевые элементы 5 установки кода подключены к установочным входам дополнительного управляемого делителя б частоты, формирователь

7, элементы И 8 и 9, один из входов которых подключен к выходу триггера 10, триггер 11, подключенный к одному из входов схемы И

12, выход которой подключен к последовательно соединенным триггерам 13 — 15, элемент И

16, установленный на входе счетчика периодов

17, потенциальные выходы всех разрядов которого подключены к дешифратору нуля 18, выход которого подключен к последовательно соединенным формирователю 19 и триггеру

20, триггер 21, выход которого соединен с одним из входов элемента И 22, выход которого подключен к элементу 23 задержки через элемент ИЛИ 24, другой вход которого соединен с входом делителя 25 частоты, выходы которого подключены к соответствующим входам элементов И 26 и 27, другие входы которых подключены к выходам триггера 28, при этом выходы элементов И 26 и 27 подключены к входам элемента ИЛИ 29, выход которого соединен с входом элемента И 9 блока управления 30, включающего в себя элементы И 1, 8, 9,12, 16, 22, триггеры 10, 11, 13, 14, 15, 21, элемент 23 задержки и формирователь 7, Перед началом работы все триггеры, делители частоты и счетчики устанавливаются в исходное, нулевое состояние. При этом с триггера 10 на элементы И 8 и 9, с триггера 11 на элемент И 12 и с триггера 15 на элементы И

1 и 16 подается сигнал, запрещающий прохождение опорной частоты через элемент И 1 на счетчик 2 периодов опорной частоты, через элемент И 8 на основной управляемый делитель 4 частоты, через элемент И 9 на дополнительный управляемый делитель б частоты, а также запрещающий прохождение входной частоты на счетчик 17 периодов входной часто5

50 ты. По команде «запись», подаваемой на вход триггера 11, последний переходит в состояние обратное исходному, при этом на один из входов элемента И 12 поступает потенциальный сигнал разрешения. Сигнал входной (запоминаемой) частоты последовательно проходит элемент И 12, счетные триггеры 13 и 14 и поступает на вход триггера 15. При этом осугцествляется пропуск первого импульса с целью привязки начала и конца измерения к переднему фронту сигнала входной частоты.

В момент поступления сигнала на вход триггера 15, последний переходит в состояние, обратное исходному, и выдает потенциальный сигнал разрешения на элементы И 1 и 16. При этом одновременно начинается счет импульсов входной частоты счетчиков 17 импульсов и счет импульсов опорной частоты счетчиком 2 периодов.

При заполнении всех разрядов счетчика 17 входной частоты, то есть при отсчете числа импульсов, равного п=2г, где P — число разрядов счетчика 17 входной частоты, на входы дешифратора нуля 18 поступят потенциальные сигналы с выходов всех разрядов счетчика 17 входной частоты, при этом на выходе дешифратора нуля 18 появится сигнал, который через формирователь 19 поступит на вход триггера 20. Последний изменит свое состояние на обратное исходному и с его выхода поступит потенциальный сигнал запрета на элементы И 1 и 16, при этом прекратится с ет импульсов входной частоты счетчиком 17 и счет импульсов опорной частоты счетчиком 2 периодов, на котором будет зарегистрировано число, равное

Л = foa Твх и (1) где f«частота опорного сигнала;

Т„. — период входного сигнала, равный

1 I

Fax

n — число импульсов, зарегистрированное счетчиком 17 импульсов входной частоты.

Одновременно с подачей на элементы И 1 и 16 сигнала запрета этот же сигнал подается на формирователь 7. Сформированный формирователем 7 импульс поступает на входы ключевых элементов 3 и 5 и кратковременно открывает их, при этом происходит запись числа Л" в основной управляемый делитель 4 частоты, и числа N2 в дополнительный управляемый делитель б частоты, где Л вЂ” число, зарегистрированное старшими разрядами счетчика 2.

На этом заканчивается цикл записи. Число, записанное в счетчике 2, может храниться значительное время и быть использовано при необходимости воспроизведения входной частоты.

При воспроизведении входной частоты на вход триггера 21 подается сигнал «воспроизведение», при этом триггер 21 изменит свое состояние на обратное исходному и с его вы5729!8 хода поступит сигнал разрешения на элемент

И 22. При поступлении сигнала разрешения на элемент И 22 первый же импульс опорного сигнала, пройдя элемент ИЛИ 24, поступит одновременно на выход устройства и через элемент задержки 23 на вход триггера 10. Элемент задержки 23 осуществляет задержку выходного импульса на время, большее длительности импульса опорной частоты и меньшее ее периода.

При поступлении импульса на вход триггера 10 последний переходит в состояние, обратI!oe исходному. При этом снимается запрет с элементов И 8,9, осуществляется запрет элемента И 22 и начинается деление опорной частоты основным 4 и дополнительным 6 управляемыми делителями частоты, при этом с выхода основного управляемого делителя 4 частоты будет сниматься сигнал с частотои FI — — —, а

fon

1V с выхода дополнительного управляемого делителя 6 частоты будет сниматься сигнал с частотои Г2 =

fon гг р fon fon вх

fon 7вх п (2) fon fon 2Р г У N N, (3) N — число, записанное всеми разрядами счетчика 2 опорной частоты;

Л 1 — число, записанное младшими разрядами счетчика 2;

М2 — число, записанное старшими разрядами счетчика 2;

Т„, — период входного сигнала. где

Число PI младших разрядов счетчика 2 опорной частоты равно числу Р разрядов счетчика 17 входной частоты Р, =Р.

Сравнивая выражения (2) и (3) можно видеть, что F„= -и, а F, =

fon fon и

N N — NI

Значение частоты F> может быть равно частоте входного сигнала Г„,. только при значении числа Л,, равном нулю, однако это условие практически не выполняется, а число NI может принимать значения от 0 до (2" — 1).

При этом частота Гг будет всегда больше истинного значения входной частоты.

В зависимости от времени воспроизведения и значения числа Л11 накопленная погрешность числа импульсов может оказаться недопустимой.

Достижение высокой точности воспроизведения частоты обеспечивается стробированием частоты „снимаемой с дополнительного управляемого делителя 6 частоты, периодом сигнала, снимаемого с основного управляемого делителя 4 частоты.

При этом накопленная ошибка не будет

1 превышать погрешности за время T и—

Fax при любом времени воспроизведения. Дальнейшая работа устройства при воспроизведенни входной частоты осуществляется следующим образом.

Как было описано выше, с выходов управляемых делителей основного 4 и дополнительного 6 снимаются сигналы частотой FI и Fo соответственно. Импульсы с выхода дополнительного управляемого делителя б частоты поступают на вход делителя 25 частоты и через элемепт ИЛИ 24 на выход устройства. Делитель 25 гастоты делит входную частоту в

2пз+ раз. С потенциальных выходов делителя

25 частоты сигналы поступают на входы элементов И 26 и 27, на другие входы элементов И 26, 27 подается потенциальный сигнал с триггера 28, па вход которого постуг ают импульсы с выхода основного управляемого делителя 4 частоты. Сигналы на входах сфазировапы так, что большую часть времени на выходах элементов И 26 и 27 выходной сигнал отсутствует и появляется только прп рассогласовании входных сигналов. Этот сигнал рассогласования через элемент ИЛИ 29 поступает одновременIIо на вход элcìcíò0 11 9 и на ключевой элемент 5 установки кода.

25 Прп поступлении сигнала рассогласования на элемент И 9 осуществляется вычеркивание некоторого количества импульсов из и

1 оследовательности импульсов опорной частоты, поступающей на вход дополнительного уп30 равляемого делителя 6 частоты. 3а счет такого вычеркивания импульсов осуществляется коррекция частоты выходного сигнала.

Формула изобретения

35 Устройство воспроизведения частоты входного сип1ала, содержащее запоминающий блок, выполненный в виде счетчика периодов опорной частоты, выходы всех разрядов которого через ключевые элементы подключены к

40 устаповоч11ым входам основного управляемого делителя частоты, и блок управления с двумя сигнальными входами orrорной и входной частот, и двумя управляющими входами, первый выход которого

45 соединен с входом счетчика периодов опорной частоты, а второй и третий выходы подключены, соответственно, к управляющим входам ключевых элементов и к входу основного управляемого делителя частоты, о т л и50 ч а ю щ е е с я тем, что, с целью повышения точности воспроизведения частоты входного сигнала, в него дополнительно вьедены ключевые элементы, управляемый делитель частоты, счетчик периодов вход1 010 сигнала, де55 лптель частоты, элементы И, ИЛИ н триггеры, при этом выходы старших разрядов счетчика периодов опорной частоты через дополнительные ключевые элементы подключены к установочным входам дополнительного управ60 лясмого делителя частоты, вход которого соединен с четвертым выходом блока упразленпя, а выход подключен к первому входу первого элемента ИЛИ, к первому управляющему входу дополнительных ключевых элемен65 тов и входу делителя частоты, каждый пз по572918

9оспр

Составитель В. Войтов

Корректор Л. Денискина

Tcxpeä И. Михайлова

Редактор H. Хлудова

Заказ 1982/7 Изд. № 751 Тираж 1080 Подписное

НПО Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, К-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2 тенциальных выходов которого соединен с одним из входов соответствующих элементов

И, другие входы которых подключены к потенциальным выходам счетного триггера, вход которого соединен с выходом основного управляемого делителя частоты и дополнительным управляющим входом ключевых элементов, причем выходы элементоз И через второй элемент ИЛИ подключены к второму управляющему входу дополнительных ключевых элементов и к пятому выходу блока управления, шестой выход которого соединен со счетчиком периодов входного сигнала, выходы всех разрядов которого через дешифратор нуля, формирователь и триггер подключены к седьмому выходу блока управления, восьмой выход

5 которого соединен со вторым входом первого элемента ИЛИ, выход которого подключен к девятому выходу блока управления.

Источники информации, принятые во внимание при экспертизе

10 1. Сборник работ по вопросам электромеханики. Вып. 7, изд. AH СССР, 1962 г., с. 305 — 306.