Интегральный логический элемент

Иллюстрации

Показать всеРеферат

(ii) 572929

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Содиалистичесиих

Республик (б1) Дополнительное к авт. свид-ву (22) Заявлено 26.12.75 (21) 2308233/21 (51) М. Кл.з H 03К 19/08 с присоединением заявки Ы

Государственный комитет

Совета Министров СССР ло делам изобретений и открытий (23) Приоритет

Опубликовано 15.09.77. Бюллетень ЛЪ 34

Дата опубликования описания 03.10.77 (53) УДК 621.375.083 (088.8) (72) Авторы изобретения

1О. И. Щетинин, В. В. Воробьева, В. Я. Кремлев и О. P. Щербинина (71) Заявитель (54) ИНТЕГРАЛЬНЪ|Й ЛОГИЧ ЕСКИЙ ЭЛЕМЕНТ

Изобретение относится к области вычислительной техники.

?13Âeeò11û интсl ральпые логические элементы, прсдстаьляющис собои комбипаци1о вентиля l i i l-типа, содержащего многоэмиттерныи п фазорысщешггс,1ьныи транзисторы, и отсскающеи цепи (1). 11едостатками таких элементов являются конструктивная сложность и значитсльнос потреолснис тока от источника питания.

Известен интегральный логический элемент, В которо:ч1 Отсскаlощая цепь содержит фиксируlolllllII:ëlloãoýìèòòåðíûè транзистор, эмиттеры которого подк;почены к входам схемы, диод и два рез:1стора 21. Недостатки этого интегрального логического элемента — сложность конструкции и большая потребляемая им мощность.

Целью изобретения является конструктивное у прощение интегрального лоп1ческого элемента и уменьшение потрсблясмои им мощности. Это Достигается тем, что в интегральном л01чlчсском элсмснте, содср кащем транзисторно-транзисторные элементы И вЂ” ?1?, Выпо;!нснпыс каждыи на Входнозl многоэм1ггтерпом и фазорасщспптельном транзисторах, и фпкспрующии многоэмиттсрныи транзистор, эмпттсры которого соединены с эмиттерами входных многоэмиттерных транзисторов, коллектор фиксирующего многоэмпттерного транзнстора соединен с общей шиной, а база подключена к эмиттсрам всех фазорасщепптельных транзисторов.

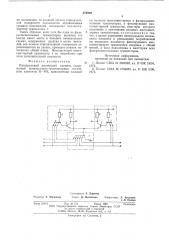

Р1н1сгральныи логический элемент представлен Ila чертеже и содержIIT мпо1оэмпттерный транзистор l огсскающей цспп, эз»ггтсры которого подсоединены к эмиттерам входных многоэмиттсрных транзисторов 2, 3, коллектор подключен к оощей шине земли, а база

10 соединена с эмпттерамп фазорасщепительных транзисторов 4, 5, и резисторы b, !, b, ?.Сл11 ко всем эм11ттерам транзисторов 2 и 3

IIpIi Io l ello напряжение логической единицы, то токи этих транзисторов открывают транзи15 сторы -4 п 5, а их токи протекают в переход база-коллектор транзистора 1, который в этом случае работает в инверсном режиме. г;сли теперь хотя бы к одному из эмпттсров в.лдного транзистора, например 2, прпло20 жить напряжение логического нуля, то фазорасщс1штсльный транзистор 4 закрывается и через переход база-коллектор транзистора 1 протекает ток только транзистора 5.

llpII наличии сигнала помехи отрицательной

25 пол51рности на Одном пз Входов элс\lента (например, на одном пз эмпттеров транзисторы 2) ток транзистора 5, текущий в базу транзистора 1, псрекл1очастся из коллскторного переxo;Iа транзистора 1 в эмпттерный. Так как

30 транзистор 1 работает в этом случае в рсжп572929

Составитель Л. Дарьина

Тсхрсд И. Михайлова

Редактор Т. 1Орчикова

Коррскторы: Л. Брахнина и Л. Орлова

Заказ 2147/1 Изд. № 773 Тираж 1080

НПО Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, >К-35, Раушская наб., д. 4 5

Подписное

Типография, пр. Сапунова, 2

М0 насыщения> то Входной crrrr13JI Отрицатсльной полярности оказывается ограниченным уровнем напряжения насыщения коллекторэмиттер транзистора 1.

Таким образом, если хотя бы один из фазорасщепительных транзисторов включен, что всегда имеет место в больших интегральных схемах, содержащих десятки и сотни вентилей, все помехи отрицательной полярности ограничиваются на уровне, примерно равном потенциалу общей шины. Фиксирующий многоэмиттерный транзистор 1 не потребляет при этом дополнительной мощности.

Формула изобретения

Интегральный логический элемент, содержащий транзисторно-транзисторные логические элементы И вЂ” HE, выполненные каждый на входном мпогоэмиттерном и фазорасщепительном транзисторах, и фиксирующий многоэмиттерный транзистор, эмиттеры которого соединены с эмиттерами входных многоэмиттерных транзисторов, отличающийся тем, что, с целью упрощения интегрального логического элемента и уменьшения потребляемой им мощности, коллектор фиксирующего многоэмиттерного транзистора соединен с общей

10 шиной, а база подключена к эмиттерам всех фазорасщепительных транзисторов.

Источники информации, принятые во внимание при экспертизе

15 1. Патент США № 3699362, кл. Н ОЗК 19/34, 1972.

2. Патент США № 3704383, кл. Н ОЗК 5/08, 1972.