Устройство интегрирования сигналов

Иллюстрации

Показать всеРеферат

О П И С А Н И Е,„м

ИЗОБРЕТЕНИЯ

Союз Советских

Социалистических баеслублик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 19.0416(21) 2346320/21 (51) М. Клл;, 06 Я 7/18 с присоединением эаявни,ле— (23) Приоритет (43) Опублиновано250977. Бюллетень ЭЙ 35 (45) Дата опубликования описания 2а10..77

Гееударатеепнб кеметет

Веаета Маааатрее ИСР ае делам еаебретеааб е етермтеб (53) УДК 681.335,7 (088.8) (72) Авторы изобретения В.д. никотин, В.В. чувыкин и В.M. 1т1пяндлн (71) Заявитель

Пензенский политехнический институт (54) УСТРОИСТВО ИНТЕГРИРОВАНИЯ СИГНАЛОВ

Изобретение относится к вычисли тельной и электроизмерительной технике и может использоваться для решения задач фильтрации и измерения интегральных характеристик сигналов. 5

Известен интегратор напряжений, содержащий ключ и операционный усилитель с емкостной отрицательной обратнбй связью fl) .

Недостатками известного интеграто- 10 ра являются низкая надежность и невысокая точность интегрирования.

Известен также интегратор, содержащий операционный усилитель с емкостной отрицательной обратной связью, IS аналоговое запоминающее устройство и тактовый генератор j2) .

Недостатком такого интегратора является наличие зависимости динамической погрешности от длительности 20 цикла преобразования.

Цель изобретения — уменьшение динамической погрешности.

Для этого в устройство интегрирования сигналов, содержащее последо- 25 вательно соединенные интегратор и аналоговое запоминающее устройство, два последовательно соединенных резистора, включенных между входом и выходом устройства, и тактовый генератор, введены делитель частоты, ждущий мультивибратор и ключ, включенный между точкой соединения резисторов и входом интегратора, а тактовый генератор через ждущий мультивибратор подключен к управляющему входу ключа и через делитель частоты — к управляющему входу аналогового запоминающего устройства.

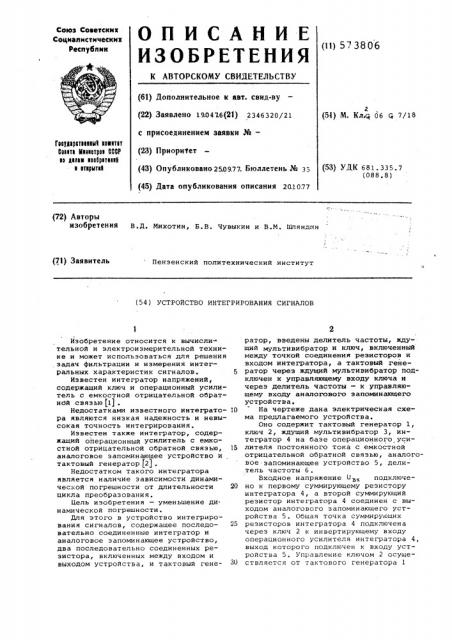

На чертеже дана электрическая схема предлагаемого устройства.

Оно содержит тактовый генератор 1, ключ 2, ждуший мультивибратор 3, интегратор 4 на базе операционного усилителя постоянного тока с емкостной отрицательной обратной связью, аналоговое запоминающее устройство 5, делитель частоты 6.

Входное напряжение 1в„ подключено к первому суммирующему резистору интегратора 4, а второй суммирующий резистор интегратора 4 соединен с выходом аналогового запоминающего устройства 5. Общая точка суммирующих резисторов интегратора 4 подключена через ключ 2 к инвертирующему входу операционного усилителя интегратора 4, выход которого подключен к входу устройства 5. Управление ключом 2 осуществляется от тактового генератора 1

573806 будет выполняться. 40 1НИИПИ ираж 818

Закаэ 3759/38

Подписное через мультивибратор 3, а управление устройством 5 осуществляется тактовым генератором 1 через делитель частоты 6

В процессе работы схемы с генератора 1 следуют импульсы с периодом Т.

С выхода делителя частоты 6 на управляющий вход устройства 5 поступают импульсы с периодом, равным и где — коэффициент деления делителя частоты),которые на короткий промежуток времени открывают ключ 7 в устройстве 5. При этом в начале каждого цикла, равного П Т, работы устройства происходит запоминани ча интег ратор 4 накопившегося нпряжения за предыдущий цикл. В каялом цикле работы устройства осуществляется интегрирование входного напряжения 1)в„ и напряжения U „,„ c выхода устройства 5. При этом под действием U выходное напряжение интегратора умень=,0 шится эа такт на величийу, равную

uâõ и-tî! 31,с. где 1, — длительность импульса, вырабатываемого ждущим мультивибратором 3; В„ — сопротивление первого суммирующего резистора интегратора, а под действием напряжения !)э возрастет на величину Пвь х и tî г0 где R> сопротивление второго суммирующего резистора интегратора. При скачкообразном изменении входного напряжения выходное напряжение !вь,х в каждом цикле работы устройства описывается раэностным уравнением где С вЂ” емкость конденсатора интегратора.

При п1 =к С равенство

ПРеимуществ,редлагаемого устрой-45 ства заключается в том, что для него условие оптимального быстродействия и-1 = Я С выполняется независимо от длительности цикла п Т интегрирования, то есть динамическая погрешность определяется только точностью выполнения равенства п.1 Я С, которое можно сделать сколь угодно точным.

Как следует из выражения (2), предлагаемое устройство представляет собой элемент задержки дискретизированного значения входного напряжения на один цикл. Достоинством предлагаемого интегратора сигналов с модуляцией является независимость динамических характеристик от длительности цикла работы, что позволяет существенно расширить его функциональные воэможности.

Формула изобретения

Устройство интегрирования сигналов, содержащее последовательно соединенные интегратор и аналоговое запоминающее устройство, два последовательно соединенных резистора, включенных между вхо. дом и выходом устройства, и тактовый генератор, о т л и ч а ю щ е е с я тем, что, с целью уменьшения динамической погрешности, в него введены делитель частоты, ждущий мультивибратор и ключ, включенный между точкой соединения резисторов и входом интегратора, а тактовый генератор через ждущий мультивибратор подключен к управляющему входу ключа и через делитель частоты — к управляющему входу аналогового запоминающего устройства °

Источники информации, принятые во внимание при экспертизе:

1. Авторское свидетельство СССР, р 332466, кл. 6 06 G 7/18, 1970.

2. Гутников В.С. Применение операционных усилителей в измерительной технике. Л., Энергия, 1975, с. 90.

Филиал ППП Патент

l г. Ужгород, ул. Проектная,4