Последовательно-параллельный ключ

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОП ИСАНИ

И3ОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТВЛЬСТВУ (! !)570876 (61) Дополнительное к авт. свнд-ву (22) Заквлено 12.04.76(21) 2348341/21 с присоединением заявки № (23) Приоритет (43) Опублнковано25.09.77.Бюллетень Юе 35 (45) Дата опубликования описания 21.10.77 (51) M. Кл.

Н 03 К 17160

Государственный комитет

Совета Мнннатрав СССР па делам нзооретеннй н откра!тнй

РЗ) УДК 821.382.С3 (088.8) (72) Автор изобретения

П. П. Втулкин (71) Заявитель (54) ПОСЛЕДОВАТЕЛЬНО-ПАРАЛЛЕЛЬНЫЙ КЛЮЧ

Изобрете!и!е относится к аналого-цифровой вычислительной технике и может использоваться в автоматике и измерительной технике.

Известен последовательно-параллельный ключ для пифро-аналоговых преобразователей (БАП), содержащий инвертор, сбгласующий и корректирующий блоки и ключевые транзисторы одного типа проводимости, эмиттеры которых объединены и подключт- 1О ны к выходу ключа, коллекторы — к полю-. сам источника опорного напряжения, а базык выходу согласующего блока (lj.

Известен также последовательно-парал- е5 лельный ключ для цифро-aíàëîãoBîro преобразователя, вход которого подключен к первому входу и через инвертор ко второму входу согласующего блока и входу корректирующего блока, содержащего конденсато- вС! ры, два выхода которого подключены к третьему и четвертому входам согласующего блока, выходы согласующего блока подключены к базам ключевых транзисторов, эмиттеры которых объединены и подключе-, ®

2 ны к выходу ключа, а коллекторы — к полюсам источника опорного напряжения r 2j.

Недостатки известных последовательнопараллельных ключей — низкое быстродействие и точность.

Цель изобретения — повышение быстродействия и точности.

Это достигается тем, что в последовательно-параллельном ключе для иифро-аналогового преобразователя, содержащем согласующий блок, корректирующий.блок на конденсаторах и ключевые транзисторы, при этом вход последовательно-параллельного ключа подключен к первому входу и через инвертор «о второму входу согласующего блока и входу корректирующ

ro блока, два выхода которого подключены к третьему и четвертому входам согласующего блока, выходы согласующего блока подключены к базам ключевых транзисторов, эмиттеры. которых объединены и подключены к выходу последовательнспараллельного ключа, ковлекторы - к полюсам источника шторного нЖтряження, согласующий блок содержит два коммутирующих транБ73876 зисторв, генераторы задающего тока и генераторы компенсирующего тока, причем база первого коммутирующего транзистора подключена к первому входу согласующего блока, в база второго - ко второму входу б согласующего блока, коллекторы коммутирующих транзисторов подключены к входам первого и второго генераторов компенсирующего тока, а эмиттеры - к входам второго и первого генераторов задающих токов соотг 10 ветственно, входы первых генераторов задающего и компенсирующего токов являют ся третьим и четвертым входами согласующего блока, а выходы первых генера-! торов задающего и компенсирующего тока 15 объединены и подключены к базе первого дополнительного ключевого транзистора р-п,-р типа проводимости эмиттер которо»

rm подключен к выходу последовательно-параллельного ключа, в коллектор — к коп- О лектору второго ключевого транзистора и к базе второго дополнительного ключевого транзистора д-$-д.(гипв проводимости,эмиттер которого подключен к объединенным выходам вторых генераторов жадвющего и Ж компенсирующего токов, а коллектор к коллектору первого ключевого транзистора.

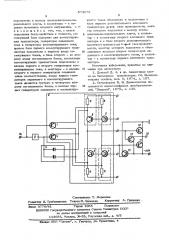

На чертеже дана принципиальная схема предлагаемого цоследоввтельно-пвраллельногэ ключа. ЗО

Вход ключа соединен с базой коммутирующего транзистора 1 согласующего блока 2 и через инв ртор 3 с базой второго коммутирующего транзистора 4 блока 2 и входом корректирующего блока 5. Коллекторы тран- 5 зисторов 1 и 4 блока 2 соединены с входами первого и второго генераторов 6 и 7 компенсирующего тока, а эмнттеры -,с входами второго и первого генераторов. 8 и 9 задающего тока соответственно. Выходы генераторов 8 и 6 задвкнйего и:компенсирующего тока объединены и подключены к базе первого ключевого трш?зйстора 10, эмиттер которого подключен к эмиттеру второго ключевого транзистора 11 и выходу ключа. Выходы генераторов 7 и 9 объединены и подключены к базе второго ключе. вого транзистора 11. Первый дополните ный ключевой транзистор 12 подключен базой к базе, эмиттером - к эмиттеру транзистора 10, коллектором - к коллектору

° транзистора 11 и к базе второго дополни тельного ключевого транзистора 13, эмиттер которого подключен к базе второго ключевого транзистора, в коллектор - к коллектору первого ключевого транзистора.

Коллекторы первого и второго ключевых транзисторов 10 и 11 подключены к по» люсам источника опорного напряжения. Схе ма содержит вход 14 и выход 15.

По .педовательно-параллельный ключ работает следующим образом.

Входной потенциал управления с входа

14 ключа поступает на базу транзистора 1 блока 2 и на вход инвертора 3, который инвертирует сигнал (если на входе ключа присутствует логическая "1", то есть высокий потенциал, то на выходе инвертора устанавливается логический "0", то есть потенциал низкого уровня).

Таким образом, на базе транзистора 4 блока 2 присутствует потенциал низкого уровня, если на базе транзистора 1 установлен высокий потенциал, и, нвоборотвысокий потенциал, если на базе транзистора 1 установлен потенциал низкого уровня, Если на входе ключа установлен высокий потенциал J коммутирующий транзистор

1 закрыт, а транзистор 4 открыт. Генераторы 8 и 7 оказываются выключенными, а транзистор 10 заперт, и ток генератора

9 поступит в базу транзистора 11, который насытится, а через коллекторный и эмитте ный переходы транзистора 12 передается в базу и на выход первого генератора 6 кпмпенсируюшего тока. Токи генераторов 9 и

6 устанавливаются равными по абсолютной величине. Потенциал базы первого ключевого транзистора 10 при этом смещен относительно потенциала эмиттерв на фиксированную величину.

Транзистор 13 заперт напряжением второго ключевого транзистора.

Боли s-в вход ключа подан потенциал низкого уровия, транзистор 1 открыт, а тоанзистор 4 закрыт. Выходной ток гене ратора 8 поступает в базу транзистора 10 и черж переход коллектор-эмиттер транзистора 13 поступает на выход генератора

7 компенсирующего тока. Величина токов генераторов 7 и 8 устанавливаются равными по абсолютной величине.

Формула изобретения

Последовательно-параллельный ключ для цифро-аналогового преобразователя, содержащий соглегующий блок, корректирующий блок нв конденсаторах и ключевые транзисторы, при этом вход последовательно-параллельного ключа подключен к первому входу и через инвертор ко второму входу согласующего блока и входу корректирую»

perm блока, два выхода которого подключены к третьему и четвертому входам согласующего блока, выходы согласующего блока подключены к базам ключевых транзисторов, эмиттеры которых объединены и

573876

Составитель Т. Морозова

Редактор Л. Гребенникова Текред M. Левицкая Kopp ° Г чшенко

A. Гриценко

Заказ 3776141 Тираж 1065 Поднисное

0НИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5 филиал ППП «Патент", r. Ужгород, ул. Проектная, 4 подключены к выходу последовательно-параллельного ключа, а коллекторы †. к полюсам источника опорного напряжения, о тличаюшийся тем,что,сцелью повышения быстродействия и точности, согласукнций блок содержит два коммутирующих транзистора, генераторы задающего тока и генераторы компенсирующего тока, причем база первого коммутирующего транзистора подключена к первому входу со- 1О гласующего блока, а база второго — ко второму входу согласующего блока, коллекторы коммутирующих транзисто юв подключены к входам первого и второго генераторов компенсирующего тока, а эмиттеры — к входам 15 второго и первого генераторов задающих токов соответственно, входы первых генераторов задаюшего и компенсирующего токов являются третьим и четвертым входами согласующего блока, а выходы пер- 20 вых генераторов задающего и компенсируюшего токов объединены и подключены к базе первого дополнительного ключевого транзистора р- и-р типа проводимости, эмиттер которого подключен к выходу последовательно-параллельного ключа, а коллектор — к коллектору второго ключевого транзистора и к базе второго дополнительного ключевого транзистора tt -р-и типа проводи мости, эмиттер которого подключен к объединенным выходам вторых генераторов задающего и компенсирующего токов, а коллектор — к коллектору первого ключевого транзистора.

Источники информации, принятые во внимание при экспертизе:

1. Донской Д. А. и др. Аналоговые ключи на биполярных транзисторах. Сб. Вычислительная техника, вып. 5, 1974., с. 107. . 2. Островерхов В. В. Динамические погрешности аналогоцифровых преобразователей. Знергия, 1975., с. 148.