Синхронный логический элемент

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. саид-ву(22) ЗаЯвлено 02,04.76 (21) 2341420/21 с присоединением заявки № (23) Приоритет (43) Опубликовано 25,09.77. Бюллетень №3 (45) Дата опубликования описания 26.10.77 (1ii 573881

2 (Ь1) М. Кл.

Н 03 К 18/22

Гооударственнмн номнтет

Совета 1йнннотрое СССР но делам наооретеннй н аткрмтнй (53) УДК 681.327 (088.8) Ь, Г,,Коноплев и M Ф. Пономарев (72) Авторы изобретения

Таганрогский радиотехнический институт им, B. Д,,Калмыкова (71) Заявитель (54) СИНХРОННЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ

Изобретение предназначено для построения синхронных (динамических) устройств вычислительной техники, в частности микроэлектронных.Известен синхронный логический элемент (СЛЭ), представляющий собой триггер с нв» посредственными связямн на двух многоэмиттерных транзисторах, причем свободные от триггерных связей эмиттеры одного из транзисторов испольэуютса как входные ц пи СЛЭ. Для обеспечения установки в определенное состояние при отсутствии на входе сигналов с низким уровнем напряжения один из свободных от триггерных свизей эмиттеров второго транзистора триггера соединен через резистор с обшей шиной. Тактирование осуществляется с помощью транзисторного ключа .1 11 .

Недостатками этого элемента являются использование в схеме резисторов и необходимость создания изолированных областей дпя раэмещеняя резисторов и транзисторов при изготовлении элемента в виде микросхемы.- Bce это приводит к увеличению плошади, занимаемой элементом иа поверхности

2 кристалла, к снижению быстродействия вслед ствив влияния значительных емкостей, ре эисторов и изолирующих структур, 11ель изобретения - уменьшение мощности, потребляемой элементом от источнкка питания.

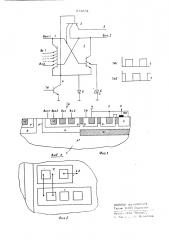

Для этого в синхронный логический tàïå мент введены двухколлвкторный транзистор, фиксирующий диод и диод с малым прямым ð падением напряжения (например, диод Шот» тки), причем эмкттер .двухколлекторного транзистора соединен с источником питания, база с, объединенными эмиттерами миан о эмиттериых транзисторов, коллекторы - с соответствующими баэамк многоэмиттерпых транзисторов, ансщ фиксирующего диода сов динен с объединенными эмиттерамя многа эмиттврных транзисторов, анод диода с ма лым прямым падением напряжения соединен

20 с одним нз свободных эмиттвров второе о многоэмиттерного транзистора, а катоды диодов соединены с общей шинойНа фиг, 1 дана приндипиальная ааектри ческая схема элементами на фиг 3 топейо»

25 гня элемента.

5 3Н>31

Синхронный логи и ский элеме т сод«ржит два перекрестно соединенные мноа оэмиттерные транзисторы 1 и 2, образующие триггер, токозадающий транзистор 3, ключевой транзистор 4ю фиксирующий диод 5 (Ю ) и диод 6 с малым прямым падением напряжения (Dg), Источник питающего напряжения включается между эмиттером транзистора 3 и общей шиной. Тактовые импульсы подаются на базу транзистора 4. Входные логические сигналы подаются на свободные от триггерных связей эмиттера транзистора 1, а выходныеснимаются с коллекторов транзисторов 1 и

2ф

Элемент может работать в режиме хра.нения (транзистор 4 насыщен при подаче импульса.Тя ) и в режиме установки (транзистор 4 закрыт), И режиме хранения, потенциала на входных эмиттерах элемента, соединенного с аналогичными элементами второй фазы тактовых импульсоь, могут изменяться от U до Е (U

Г

k напряжение на диоде,з при закрытом транзисторе 4), Так как потенциал объединенных эмиттеров транзисторов 1 и 2 равен изменение логических состоя .этч.нлс ний элементов второй фазы ТИ не изменяет состояние рассматриваемого элемента, так как 13 3, Е У„ „ " р - и - переходы 30 входных эмиттеров заперты (J„ .. . -напряжение насыщения транзис-ора 4), В режиме установки потенциал объединен.ных эмиттеров равен У, а потенциалы входных эмиттеров могут изменяться от 35

Ug.y>q, äñ до Е

Если хотя бы один из входных эмиттеровимеет потенциал У, тс р - и переход этого эмиттера открыт и базовый ток отводится от транзистора 1 на общую шину, транзистор 1 выключается, транзистор 2 включается

Если все входные эмитгеры имеют потекциал Е, то транзистор 1 включается, а транзистор 2 выключается, так как базовь и ток отводится от транзистора 2 через диод 6 на общую шину, Условие работоспособности элемента запишется в виде сЦ k.9тЧ. нАс D2 ВФ

Из приведенного выше ясно, что элемент ре ал иву е т логическую фу нкшпо И / И- ИЕ, Из приведенной на фиг, 2 топологии СЛЭ ьпдп", «ru схема элемента позволяет выполнить все элементы одной фазы ТИ в обшей изоли о..апной области, причем подложка является эмиттером транзистора 3, обслуживаюпюго элементы обеих фаз. Ключевой транзистор 4, диод 5, база транзистора 3 — общие для элементов одной фазы ТИ, Коллекторы транзистора 3 являются базами транзисторов 1 и 2. Ьаза транзистора 3 является эмиттером транзисторов 1 и 2 и коллектором транзистора 4, Отсутствие резисторов, совмещение функ ций нескольких компонентов в одной полупроводниковой области обеспечивает высс кую степень интеграции при изготовлении элемента в составе И, дает выигрыш в быстродействии при равной с известным элементом потребляемой мощности, 4

Применение предлагаемого синхронного логического элемента СПЭ для создания интегральных цифровых устройств позволит уве личить степень интеграции элементов на кристалле, увеличить быстродействие и уменьшить потребляемую элементом мощность.

Формула изобретения

Синхронный логический элемент, содержащий два многоэмитгерных транзистора, коллекторы которых перекрестно соединены с базами, один из эмиттеров каждого многоэмиттерного транзистора соединен с коллекTopDM биполярного TpBHBHc i, ора, ВМНТТ8р K&4 торого соединен с обшей шиной, а база — с тактовым входом элемента, свободные эмичтеры первого многоэмиттерного транзистора соединены с входными шинами элемента, отличающийся тем, Что, с целью уменьшения потребляемой мощности, в наго введены двухколлектсрный транзистор, фиксирующий диод с малым прямым падением напряжения (например, диод Шоттки), причем эмиттер, двухколлекторного транзистора соединен с источником питания, база — с. объединенными эмиттерами многоэмиттерных транзисторов, коллекторы — с соответствующими базами многоэмитгерных транзисторов, анод фиксирующего диода соединен с объединенными эмиттерами многоэмиттерных транзисторов, анод диода с малым прямым падением напряжения соединен с одним из свободных эмиттерсв второго многоэмиттерного транзистора, а катоды диодов соединены с обшей шиной.

Исто ники информации, принятые во внимание при экспертизе;

1, Микроэлектроника, Под,ред, Л, А, Васепкова, вып, 8, М„, "Советское радио", 1975, с. 1,,Q,