Интегральный пороговый логический элемент с разрядовой связью

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К МЗТОРСКОМУ СВИДЕТЕЛЬСТВУ (и) 573882 (61) Дополнительное к авт. свид-ву (22) Заявлено 0904.76 (21) 2347080/21 с присоеттинением заявки №вЂ” (23) Приоритет (43) Опубликовано 2509.77. Бюллетень № 35 (45) Дата опубликования описания 29.1077 (5!) М. Кл.

Н 03 K 19/28

ГсстдсрстссссиЧ ссмстст

Сссста с(сссстрсs СССР сс ссссв исс1рстсссс с стирытсс (53) 11К 82 ) ° 382 (088. 8) (2) Лвт"р" изобретения

Б.N. Хотянов и В.А.Шилин (71) Заявитель

Московский институт электронного машиностроения (54) интеГРАльный пОРОГОВый лОГический элемент

С ЗАРЯДОВОЙ СВЯЗЬЮ

Изобретение относится к импульсной технике.

Известен пороговый логический элемент с зарядовой связью, содержащий подложку, на которую нанесены диффу- 5 зионные обл- ñòè,, входные затворы,,разде;ительнЫе слои, накопительные области ().g .

Однако известный пороговый элемент не обеспечивает требуемой стабильности, при этом мало число реализуемых логических функций.

Наиболее близок к изобретению интегральный пороговый логический элемент, содержащий входные диффузионные слои с проводимостью противоположной проводимости подложки, между которыми расположены нходные затворы, разделительные затворы, сумжирующий затвор, 33 выходные диффузионные слои, один из

KoTopblx связан с сумьырующим затвором, а второй связан с передающим затвором, и вторые разделительный и накапливающий затворы, расположенные 25 между вторыми упомянутыми диффузионными слоями (21 .

Недостатк6м такого элемента является недостаточное число реализуемым логических функц „й. 30

Цель изобретения — расширение числа реализуемых логических функций.

Это достигается тем, что н логический элемент, содержащий входные диффузионные слои с проводимостью противоположной проводимости подложки, между которыми расположены входные затворы, разделительные затворы, суммирующий затвор, выходные диффузионные слои, один из которых снязан с сумьмрующим затнором, а второй связан с передающим затвором, н вторые разделительный и накапливающий затворы, расположенные между вторыми упомянутыми диффузионными слоями, введены плавающий затвор элемента носстанонления, расположенный между вторым входным диффузионным слоем и вторым из упомянутых разделительных затворов, затворы и диффузионные слои стоков подготавливающих Мдн-транзисторов, связанные с выходными диффузионными слоями.

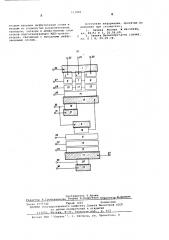

На чертеже дана структурная электрическая схема предлагаемого элемента.

Элемент содержит диффузионные области 1 и 2, служащие исто никами зарядов (все диффузионные обив<-ти имеют проводимость противополс жиую роводи573882 мости подложки), входные затворы 3, 4 и 5, на которые подаются входные логические (двоичные) сигналы, разделительные затворы 6, 7, 8 и 9, накапливающие затворы 10, 11, 12 и 13, суммирующий затвор 14, передающий затвор 15, выходные плавающие диффузионные области 16 и 17, плаваю дий затвор 18 элемента восстановления и затворы 19 и 20 и диффузионные области стоков 21 и 22 подготавливающих

ИДП-гранзисторов.

На входы 23-?5 поданы входные сигналы, на входы 26-36 — сигналы упранления H пи,алания. Выходной сигнал сни!

8 ма .тся с выхода 37. Исто .ники сигналов и питания на чертеже не покаэаны, Пороговый элемент работает следующим образом.

f3 момент времени k< разделительные затворы б, 7 и 8 открыты и иэ диФФузионной области 1 в затворы 10, 11 и 12 инжектируются или не инжектируются зарядовые пакеты в зависимости от значений логических сигналов на соответствующих входах (для определенности рассматриваются tt -канальные приборы, для р -канальных приборов все напряжения — отрицательные). Если на каком-либо входе 23-25 действ ет сигнал Логической едини- З0 цы, го соответствующий входной затвор (3, 4 или 5) открыт и в соответствующем затворе 10, 11 или 12 накаплинается заряд, пропорциональный площади затвора. Если на вход посту- 35 пает сигнал Логического нуля, то входной затвор (3-5) закрыт и зарядовый пакет в соответствующем затворе 10, ll или 12 будет отсутствовать.

В момент времени t разделитель- 40 ные затворы б, 7 и 8 закрываются и заряды в затворах 10, 11 и 12 изолируются.от нходных цепей. С приходом импульса подготовки (в момент г. ) открывается подготавлинающий КДП-тран — 45 зистор с затвором 19, .стоком 21 и областью 16 и выходная диффузионная область 16 заряжается до исходного напряжения Е. По окончании импульса диффузионная область 16 и связанный с ней затвор 18 переводятся в плавающий режим.

С поступлением импульса на вход и окончанием импульса на входе (момент

Й ) заряды из затворов 10, 11 или 12 передаются в суммируюший затвор 14 и затем (по окончании импульса) — в диффузионную область 16.

Таким образом, потенциал плавающей диффузионной области 16 и связанного с ней затвора 18 определяется Е) суммарным зарядом, накопленным в затворах 10, 11 и 12 в момент 4< . С приходом очередных импульсов из диффузионной области 2 в накаплинаюший затвор 13 инжектируется или не инжек- 65 тируется зарядовый пакет н зависимостии от потенциала затвора (8, то есть от суммарного заряда диффузионной области 16. Если суммарный заряд превышает определенную пороговую величину, то затвор 18 закрыт и накопления заряда в затворе 13 не происходит . Если же суммарный заряд меньше пороговой величины, то из области

2 н накапливаюший затвор 13 инжектируется заряд Логической единицы через канал под затворами 18 и 9.

Дальнейшая передача заряда по цепочке 13, 15 и 17 происходит аналогично описанному выше. Элементы 13 и .15 введены для согласования по тактам выхода данного элемента со входами следующих элементов.

С выхода - диффузионной области

17 - двоичный сигнал может непосредственно подаваться на входы аналогичных элементов.

Задавая соответстнуюшую неличину напряжения питания Е, можно регулировать величину порога. Если для всех пороговых элементов значения порогов Т> одинаковы, то вместо спе циального напряжения Е на диффуэионны .>области стоков 21 и 22 можно подавать подготавливающий импульс, верхний уровень которого будет определять порог.

Предлагаемый пороговый элемент позволяет улучшить характеристики интегральных схем. Выигрыш в степени интеграции, потребляемой мошности, стоимости обуслонлен преимуществом элемента перед биполярными как по соответствующим электрическим характеристикам, так и с точки зрения технологни их изготовления (технология значительно проще и обеспечивает больший выход годных приборов).

Формула изобретения

Интегральный пороговый логический элемент с зарядовой связью, содержащий входные диффузионные слои с проводимостью противоположной ачроноди— мости подложки, между которыми расположены входные затворы, разделительные затворы, суммируюший затвор, выходные диффузионные слои, один из которых связан с суммируюшим затвором, а второй связан с передающим затвором, и вторые разделительный и накапливающий затворы, расположенные между вторыми упомянутыми диффузионными слоями, о т л и ч а ю ш и и с я тем, что, с целью расширения числа реаЛизуемых логических функций, н него введены планаюший затвор элемента восстановления, расположенный между

5 73882!

2d

Составитель Т.Аотюх

Редактор Л.1 ебенникова Тех ед Й.Андрейчук Ко екто И.демчик

Заказ 3777/42 Тира к 1065 Подписное

1111ИИПИ осударстненного комитета Совета Министров СССР по делам изобретений и открытий

l l 303 5Noi x вeа a5-35 а шская на,, д

Филиал ППП Патент, г. У кгород, ул. Проектная, 4 вторым входным диффузионным слоем и вторым нз упомянутых разделительных затворов, затворы и диффузионные слои стоков подготавливающих МДП-транзисторов, câÿçàííûå с ныходными диффузионными слоями.

Источники информации, принятые во внимание при кспертизе

1. Заявка Японии Ю 44-50244, кл. 99(5) Е 3, 26.06.69.

2. Заявка Великобритаии 136449, кл. И 1 К, 09.09.74.