Логический элемент "не"

Иллюстрации

Показать всеРеферат

ОПИСАНИЕИЗОБРЕТЕНИЯ

Союз Советских

Социалистических

Республик (11) 573884

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Jlîïîëíèòåëbíîå к авт. саид-ву (22) Заявлено09,04.76 (21) 234 )98y2) с присоединением заявки № (23) Приоритет— (43) Опубликовано 2509.77 Бтоллетень № 35 (45) Дата опубликования описания 29.а077

2 (51) М. Кл.

H 03 V 19/40

Говрдарвтввнный ноинтвт

Совета Мнннвтров CCQP но долам наобрвтвннй н отнрытнв (53) УДК 2 1. 375. 3 (088.8) (72) Автор изобретения

Б.М.Хотянов (71) Заявитель московский институт электронного машиностроения (54) лОГическиЙ элемент не

Изобретение относится к импульсной технике.

Известен логический элемент НЕ, содержащий последовательно включенные активный МДП-транзистор с обогащением и нагрузочный МДП-транзистор, точка соединения которых служит выходом схемы, конденсатор, одной своей обкладкой подключенный к затвору нагрузочного МДП-транзистора, и МДП-транзистор, исток которого соединен с затвором нагрузочного МДП-транзистора, а затвор и сток подключены к источнику питания.

Этот логический элемент не обеспечивает надлежащего быстродействия.

Известен также логический элемент

НЕ, содержащий активный МДП-транзистор с обогащением, соединенный последовательно с нагрузочным МДП-тран- 20 зистором, причем точки их соединения подключены к выходу элемента, зарядный МДП-транзистор, исток которого соединен непосредственно с затвором нагрузочного ИДП-транзистора и через конденсатор - со входом элемента, а затвор и сток подключены к источнику питания(2) .

Известныи логический элемент не .обеспечивает необходимой длительно--,р стн задержки выходного импульса относительно входного.

Дель изобретения — увеличение длительности задержки выходного импульса относительно входного и амплитуды выходного логического сигнала.

Это достигается тем, что в логический элемент НЕ, -одержащий активный ИДП-транзистор с обогащением, соединенный последовательно с-нагрузочным МДП-транзистором, причем точки нх соединения подключены к выходу элемента, 3арядный МДП-транзистор, исток которого соединен непос1-:дствеино с затвором нагрузочного МДП-транзистора и через конденсатор - co входом. элемента, а затвор и сток подключены к источнику питания, введены два дополнительных МДП-транзистора, исток первого дополнительного МДПтранзистора соединен со входом элемента, его сток соединен с затвором; активного МДП- транзистора с обогащением, а затвор первого дополнит ельного МДП-т1ранзистора соединен с источником питания, причем затвор второго дополнительного МДП-транзистора сое-, динен со стоком первого дополнитель« ного транзистора, сток второго дополнительного МДП-транзистора под573884 ключен к затвору нагрузочного МДПтранзистора, а исток второго дополнительного МДП-транзистора соединен с общей шиной, параллельно нагрузоч— ному МДП-транзистору включен третий

8 дополнительный МДП-транзистор, затвор которого соединен с источником питания. !

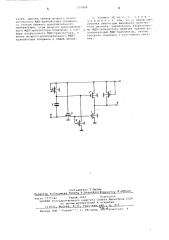

1а чертеже приведена принци пи альная схема элемента.

Элемент содержит активный МДП-транзистор с обогащением 1, нагрузочный

КДП-транзистор 2, конденсатор 3, заряжающий МДП-транзистор 4, дополнительные МЩ-транзисторы 5, 6, дополнительный нагрузочный МДП-транзистор

7. Па вход 8 поданы входные импульсы,, выходной сигнал снимается с выхода

Источники сигналов на чертеже не показаны.

Элемент работает следующим образом.О

1<огда на входе действует напряжение логического нуля ®, . - U, где пороговое напряжение МДП-структуры, МДП-транзисторы 1, 6 закрыты, а напряжение логической единицы 25 на выходе 9 инвертора составляет

F. — 2 U„ . При этом МДП-транзистор 4 находится на границе запирания, а конденсатор 3 заряжен до напряжения близкого к F - 11„ (для определенности 30 рассма риваются МДП-транзисторы с каналом 1.1 -типа, для р -канальных приборов все напряжения отрицательные).

При поступлении ступенчатого отпирающего входного сигнала МДП-транзистор 4 запирается. Поскольку МДП-транзистор 5 обладает определенным сопротивлением, фронт нарастания напряжения на затворах МДП-транзисторов 1, 6 оказывается задержанным относительно положительного фронта входного сигнала. Поэтому на начальном этапе переходного .процесса разность потенциалов между обкладками конденсатора 3 сохраняется неизменной (Равной Е -U ) 45 о и все приращение напряжения на входе передается, так как разряжающий МДПтранзистор 6 закрыт, а емкость конденсатора 3 выбирается значительно большей паразитных емкостей схемы.

Поскольку активный МДП-транзистор 1 вначале также закрыт, напряжение на выходе повышается после увеличения напряжения на затворе нагрузочного

МДП-транзистора 2, стремясь к уровню

Е. По мере нарастания напряжения на затворе МДП-транзистора 6 конденсатор

3 начинает разряжаться через него, причем постоянная времени разряда определяется сопротивлением этого транзистора и величиной емкости кон- 60 денсатора 3, а конечный уровень отношением сопротивлений МДП-транзисторов 4 и 6; одновременно с этим падает сопротивление активного МДП1транзистора 1. В результате рост на- гя пряжения на выходе сна ала замедляется, а затем напряжение спадает до уровня логического нуля, определяемого отношением сопротивлений активного 1 и нагрузочного 2 транзи— сторон, причем длительность спада определяется сопротивлением МДП-транзистора 1 и емкостью нагрузочных схем (не показаны), подключенных к инвертору. Таким образом, время задержки выходного сигнала относительно входного отпирающего сигнала представляет собой промежуток времени, в течение которого напряжение на выходе превышает первоначальный уровень логической единицы, оно зависит от постоянной времени разряда последовательно включенных конденсатора 3 и

МДП-транзистора 6.

Г!ри поступлении на вход схемы ступенчатого запирающего сигнала конден— сатор заряжается через МДП-транзистора 4 до напряжения близкого к E -U

Одновременно с этим входные емкости

МДП-транзисторов 1,5 разряжаются через МДП-транзистор 5 (что приводит к их запиранию), а напряжение на выхо де повышается до уровня логической ед ".:аицы .

Элемент позволяет обеспечить задержку выходного сигнала относительно входного отпирающего сигнала, которая часто требуется при построении встроенных МДП-формирователей тактовых импульсов, управляющих динамическими схемами со структурой МДП (в частности, приборами с зарядовой связью) .

При этом практически не увеличивается длительность фронтов нарастания и спада выходного сигнала (то есть практически не ухудшается быстродействие инвертора) .

Формула изобретения

1. Логический элемент НЕ, содержащий активный МДП-транзистор с обогащением, соединенный последовательно с нагруэочным МДП-транзистором, причем точки их соединения подключены к выходу элемента, зарядный МДПтранзистор, исток которого соединен непосредственно с затвором загрузочного МДП-транзистора и через конденсатор — со входом элемента, а затвор и сток подключены к источнику питания, отличающийся тем, что, с целью увеличения длительности задержки выходного импульса относительно входного, в него введены два дополнительных МДП-транзистора, исток первого дополнительного МДП-транзи.стора соединен со входом элемента, его сток соединен с затвором активного МДП-транзистора с обогащением, а затвор первого дополнительного МДПтранзистора. соединен с источником пи573884

Составитель Т.Артк х

Редактор В. Раакккова текРед н. Акдреекук кооректоР

Заказ 3777/42 Тирам 1065 Подписное

11111111ПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035 Москва Ж-35 Ра шская наб. д. 4/5

l. я ь Х

+4:ж=М

Филиал ИИП Патент, r. У:огород, улЪ=Проектная т 4 тания, причем затвор второго дополнительного МДП-транзистора соединен со стоком первого дополнительного транзистора, сток второго дополнительного МДИ-транзистора подключен к затвору нагруэочного МДП-транзистора, а исток второго дополнительного МДПтранзистора соединен с общей шиной.

2. Элемент 11Е по и. 1, о т л и ч а ю шийся тем, чт.,с делью увели ения амплитуды выходного логитrec:— кого сигнала, параллельно нагрузочному МДП-транзистору включен третий дополнительный МДП-транзистор, затвор которого соединен с истР чником питания.