Устройство для оперативного контроля каналов связи

Иллюстрации

Показать всеРеферат

Q ll N C A H H E

КЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Соьоэ Советских

Сощиаяистических аьеспубяии (») 57 3888 (61) Дополнительное к авт. санд-ву (22) Заявлено 080575 (2!) 2135292/09 с присоединением заявки М (23) Приоритет (43) Опубликовано 250977. Бюллетень È35 (45) Дата опубликования описания: 29.1077 (51) М. Кл.

Н 04 В 3/04

Геерларвтвваиыя ааматет

Совета Нввветрав СССР

60 Сеавьь вьееретыев а еткрнтай(53) УДК 621. 391. 833 (088.8) (72) Авторы изобретении

A. И, Штульман В.A.Êîãàí, Л.И. ярославский и И.С.Усов (71) Заявитель ключен к разрешающему входу блока on ределения коэффициента ошибок.

Прн этом блок опрецелення коэффициента ошибок содержит блок памяти, блок управления, выХоды которого соединены с входами блока индикации, управляющие выходы блока памяти под ключены к управляющим входам блока управления, к запрещающим входаМiKo10 торого подключены запрещающие выходы блока памяти, а блок памяти содетржит триггеры,.элементы ИЛИ, блок выделения фронта импульсов и блок сбрфса, причем входы "Установка 0 " триг15 геров объединены и подключены к выходу первого элемента ИЛИ, к одному из входов которого подключен вход

"Установка 1 " соответствующего триггера, к которому подключен первый

20 вход второго элемента ИЛИ, ко второму входу которого и ко второму входу первого элемента ИЛИ подключен выход блока сброса, к третьему входу второго элемента ИЛИ подсоединен

25 выход блока выделения фронта импуль сов, а третий вход первого элемента

ИЛИ является входом сброс, блока памяти.

На фиг. 1 приведена блок-схема предлагаемого устройства для операИзобретение относится к технике связи и может использоваться при измерении цостоверностн передачи дискретной информации.

Известно устройство для оперативного контроля каналов связи, содержащее последовательно соединенные входной согласующий...блок, анализатор входных импульсов и.счетчик ошибок.

Однако оно обладает недостаточной точностью контроля каналов связи..

Для устранения указанного недостатка в устройство для оперативного контроля каналов связи согласно изобретению введены блок разрешения счета, счетчик тактовых импульсов и блок определения коэффициента ошибок. Управляющий выход счетчика ошибок подключен к входу блока определения коэффициента ошибок, разрешающий выход через госледовательно соединенные блок разрешения счета и счетчик такТовых импульсов, на другой вход которого поданы тактовые импульсы, — к информационным вхььдам блока определения коэффициента ошибок, выход которого подключен к выходам сброса счетчика сшибок и блока разрешения счета, а разрешающий выход счетчика ошибок под (54) УСТРОЙСТВО 1ЛЯ ОПЕРАТИВНОГО КОНТРОЛЯ

КАНАЛОВ СВЯЗИ

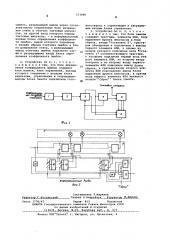

573888 тинного контроля каналов связи; на фиг 2 — структурная электрическая схема блока определения коэффициента ошибок .

Устройство для оперативного конт- 5 роля каналов связи содержит последовательно соединенные входной согласующий блок 1, анализатор 2 входных импульсов, счетчик 3 ошибок, последовательно соединенные блок 4 разреше- 10 ния счета и счетчик 5 тактовых импуль. сов, а также блок б определения коэффициента ошибок. Управляющий выход счетчика 3 ошибок подключен к входу блока б определения коэффициента оши. бок, а разрешающий ныход через последовательно соединенные блок. разрешения @чета 4 и счетчик 5 тактовых импульсов, на другой вход которого поданы тактовые импульсы, — к информационным входам блока б определения коэффициента ошибок, выход которого подключен к входам .сброса счетчика 3 ошибок и блока 4 разрешения счета.

Разрешающий выход счетчика 3.ошибок подключен также к разрешающему входу блока б определения коэффициента оши бок.

Блок определения коэффициента оши бок (фиг. 2) содержит блок памяти 7 и блок управления 8, выходы которогс соединены с входами блока индикации

9. Управляющие и запрещающие выходы блока памяти 7 подключены соотнетственно к управляющим и запрещающим входам блока управления 8. 35

Блок памяти 7 содержит триггеры

10, элементы ИЛИ 11, 12, блок 13 выделения фронта импульсов и блок сброса 14. Входы Установка 0 триггеров

10 объединены и подключены к выходу 40 первого элемента ИЛИ 11, к одному из входов которсго подключен вход "Установка 1 " соответствующего триггера

10, к которому подключен. первый вход второго элемента ИЛИ 12, ко второму входу которого и ко второму входу первого. элемента ИЛИ 11 подключен выход блока сброса 14. К третьему входу второго элемента ИЛИ 12 подсоединен выход блока 13 выделения фронта им- 80 пульсов, а третий, вход первого элемента ИЛИ 11 является входом "Сброс блока памяти 7.

Устройство работает .следующим образом. 56

Принятая информационная последовательность поступает через входной согласующий блок 1 в анализатор 2, обнаруживающий ошибочно принятые элементы сигнала и формирующий импульсы ошибок, которые поступают на вход счетчика 3. При поступлении первого импульса ошибки на вход счетчика 3 сиг нал " 0 " поступает на управляющий вход блока 4 разрешения счета.

При поступлении с выхода счетчика

3 импульса, сообщающего о появлении первой ошибки, блок 4 разрешения счета разрешает подсчет тактовых импульсов счетчиком 5 и импульсы начинают продвигаться по счетчику 5.

Одновременно с разрешением счета управляющий импульс поступает на вход сброса блока б определения коэффициента ошибок, переводя через элемент

ИЛИ 11 триггеры 10 н состояние " 0 ".

При появлении импульса на выходе счетчика 5 триггеры 10 устанавливают ся в состояние "1 " и на первый вход элемента ИЛИ 11, 12 подается потенциал 1, на второй вход каждого элемента ИЛИ 11, 12 поступает потенциал

" 1 " с инверсного выхода соответствующего триггера 10. Элементы ИЛИ 11 12 последовательно подготавливаются к выдаче сигнала в блок индикации 9.

Если на выходе анализатора 2 появляется второй импульс ошибки, то он переписывает 0 .с выхода счетчика 3 через блок памяти 7 на соответствующий вход блока управления 8, разрешая появление импульса на соотнетстнующем входе блока индикации 9.

Переход потенциала из " 1 " н " 0 ", поступающий при выдаче сигнала о второй ошибке с выхода счетчика 3 на разрешающий вход блока б определения коэффициента ошибок, поступает также на блок 13 выделения фронта импульсов.

Выделенный импульс проходит через элемент ИЛИ 12 на выход блока б определения коэффициента ошибок и переводит блок 4 разрешения счета н состояние, запрещающее подсчет импульсов счетчиком 5. Одновременно этот сигнал сбрасывает в исходное состояние счетчик 3, подготанливая его к приему импульса новой ошибки.

Описанное устройство позволяет вести непрерывный контроль за состоянием канала связи в системах передачи дискретной информации, в системах, имеющих различные скорости передачи, а также запоминать наиболее низкое значение коэффициента ошибок в канале связи.

Формула изобретения

1. Устройство для оперативного контроля каналов связи, содержащее последовательно соединенные входной согласующий блок, анализатор входных импульсов и счетчик ошибок, о т,л и ч а ю щ е е с я тем, что, с целью повышения точности контроля, в него введены блок разрешения счета, счетчик тактовых импульсов и блок определения коэффициента ошибок, управляющий выход счетчика ошибок подключен к входу блока определения коэффициента

573888

ГРЯЯОВьп ниЩЯФсм

Инфорд иаю пос Cdpoc"

Составитель Т.Маркина

Редактор Г.Котельский Техред Н.Андрейч к Корректор М.демчик

Заказ 3778/42 Тираж 815 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытиЯ

113035 Москва, Ж-35 Раушская наб. g. 4 5

Филиал ППП Патент, r. Ужгород, ул. Проектная, 4 ошибок, разрешающий выход через последовательно соединенные блок разрешения счета и счетчик тактовых импульсов, на другой вход которого поданы тактовые импульсы, — к информационным входам блока определения коэффициента ошибок, выход которого подключен к входам сброса счетчика ошибок и блока разрешения счета, а разрешающий выход счетчика ошибок подключен также к разрешающему входу блока определения коэффициента ошибок.

2. Устройство по п. 1, о т л и ч а ю щ е е с я тем, что блок определения коэффициента ошибок содержит

15 блок памяти, блок управления, выходы которого соединены с входами блока индикации, управляющие и запрещающи выходы блока памяти подключены соот20 ветственно к управляющим и запрещающим входам блока управления.

3. Устройство по п 2, о т л и ч а ю щ е е с я тем, что блок памятв содержит триггеры, элементы ИЛИ, блок выделения фронта импульсов и блок сброса, входы "Установка 0 ", триггеров объединены и подключены к выходу первого элемента ИЛИ, к одному из входов которого подключен вход Установка 1 " соответствующего триггера, к которому подключен первый вход второго элемента ИЛИ, ко второму входу которого и ко второму входу первого элемента ИЛИ подключен выход блока сброса, к третьемувходу второго элв мента ИЛИ подсоединен выход блока выделения фронта импульсов, а третий вход первого элемента ИЛИ является входом Сброс блока памяти.