Цифровой частотно-фазовой детектор

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСИОМУ СВйдЕТЕЛЬСТВУ

11Ц 574864

Союз Советских

Социалистических

Республик (61) Дополнительное к авт. свид-ву (22) Заявлено 16.02.76 (21) 2326883/09 с присоединением заявки Л (51) . 1. 1хл. Н 04L 27/14//

Н 04L 27/22

Совета Министров СССР ло делан изобретений и открытий

Опубликовано 30.09.77. Бюллетень ¹ 30

Дата опубликования описания 16.10.77 (53) УДЫ 621.376.9 (088.8) (72) Автор изобрстсш1я

Ю. И. Алехин (71) Заявитель (54) ЦИФРОВОЙ ЧАСТОТHO-ФАЗОВЫЙ ДЕТЕКТОР

ГосУдаРственный комитет (23) Приоритет

Изобретение относится к радиотехнике и может использоваться в системах радиосвязи и измерительной технике.

Известен цифровой частотно-фазовый детектор, содержащий два основных триггера, первые выходы которых подключены ко входам узла сброса, выход которого соединен с первыми входами основных триггеров (1).

Однако известный цифровой частотно-фазовый детектор имеет низкий уровень выходного сигнала.

Цель изобретения — увеличение уровня выходного сигнала.

Для этого в цифровой частотно-фазовый детектор, содержащий два основных триггера, первые выходы которых подключены ко входам узла сброса, выход которого соединен с первыми входами основных триггеров, введены два ключа, дополнительный триггер и два блока опознавания последовательности импульсов, первые входы которых соединены со вторыми входами основных триггеров, а выходы дополнительного триггера подключены к управляющим входам ключей, информационные входы которых сосдинены со вторыми выходами основных триггеров и вторыми входами бло ков опознавания последовательности импульсов, выходы которых подключены ко входам дополнительного триггера.

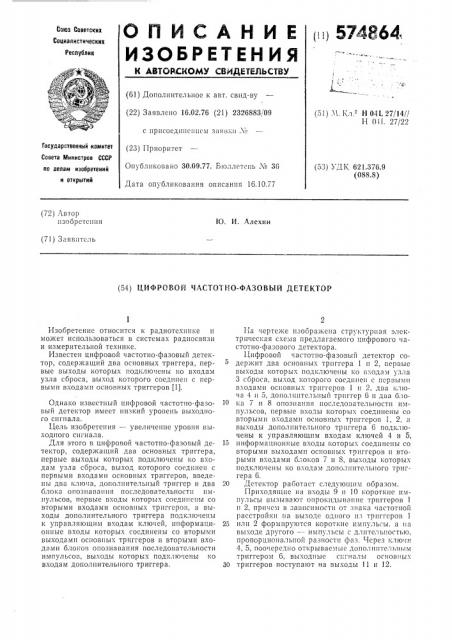

1-1а чертеже изображена структурная электрическая схема предлагаемого цифрового частотно-фазового детектора.

Цифровой частотно-фазовый детектор содер>кит два основных триггера 1 и 2, пергые выходы которых подкл1011ены ко входам узла

3 сброса, выход которого соединен с первыми входами основных триггеров 1 и 2, два ключа 4 и 5, дополнительны11 триггер 6 и два бло10 ка 7 и 8 опознания последовательности импульсов, первые входы кozopiix соединены со вторымп входами основных триггсров 1, 2, а выходы дополнительного триггера 6 подключены к управляющим входам ключей 4 и 5, 15 информационные входы которых соединены со вторыми выходами основных триггеров и втоpbIMH входами блоков 7 и 8, выходы которых подключены ко входам дополнительного триггера 6.

20 Детектор работаст следующим образом.

Приходящие на входы 9 11 10 короткие импульсы вызывают опрокидывание триггеров 1 и 2, причем в зависимости от знака частотной расстройки па выходе одного и" триггеров 1

25 илп 2 формируются короткие импульсы. а на выходе другого — импульсы с длительность1О, пропорциональной разности фаз. Через клю ьн

4, 5, поочередно открываемые дополнительным триггером 6, выходные cIii наль1 основных

30 триггеров поступают на выходы 11 и 12.

574864

Когда частота повторения импульсов на входе 9 превышает частоту повторения импульсов на в"îäå 10,,иа инверсном выходе дополнительногоого триггср а 6 устa li 3 13;»! 133 ñ Tcл высокий потенциал, а па прямом выходе — - coOT1 CTCTI3CI»1O ll II3Iil»I !IOTA!»I I!3.ч. В pC:3>>.11> гя е ключ 4 открыт, а ключ 5 закрыт.

Первый импульс, поступающий iia вход 9, Вызывает опрокидываппе основного триггера

1, и иа его первом выходе появляется высокий поте»пиал. Ila входе узла сброса 3, coegi»Icliиом с первым выходом основного трипера 2, Та! ЖЕ ВОЗНИК3ЕТ ВЫСОКИИ ПОТЕ»пи 3Л, ПОЭ 1 ОМУ перепад напряжения с основного триггера 1 проходит через узел сброса 3, воздействуя па входы сброса основных триггеров 1 и 2. Основной триггер 1 возвращается в исходное состояние, формируя на своем втором выходе короткий импульс, а иа втором выходе основ»ого триггера 2 устанавливается высокий погенцпал. Проходящий на вход 10 импульс oiiрокидывает основной триггер 2 в »сходное состояние, однако, состояние основного триггер3 1 не изменяется, поскольку прохождение перепада напряхкепия с основного триггера 2 через узел сброса 3 запрещено низким потенциалом па первом Выходе основного триггера

1. Таким образом, в течение одного периода импульсов иа входе 9 на выходе основного триггера 1 формируются короткие импульсы, а па выходе основного триггера 2 образуются импульсы с длительностью, пропорционалы!ой текущей разности фаз входных сигналов. Через ключ 4 выходной сигнал основного триггера 1 проходит на выход 11, создавая среднее значение напряжения за период входных импульсов, равное максимальному выходпому напряжению.

Описанные процессы повтрояютсл с прпходох1 каждого Вход!!Ого им пу ться до тех Ilop, пока между двумя импульсямп иа входе 10 пе оказываются двя импульса со входа 9. В этом случае импульс иа входе 9, приходящий вслед за импульсом па этом же входс, устанавливает иа инверсном выходе основного триггера 1 низкий потенциал, сохраняя состояние основного триггера 2 неизменным. Очередной импульс иа входе 10 опрокидывает основной триггер 2, п перепад папряжсппл, Ilpoходя через узел сброса 3, формирует ня его втором выходе короткий импульс. Основной триггер 1 устанавливается в состояние, соответствующее высокому потенциалу»а своем втором выходе. Теперь импульсы с длительностью, пропорциональной разности фаз, образуются на выходе основного триггера, 2, а основной триггер 1 выдает короткие импульсы. Эта последовательность работы основных триггеров сохраилется, пока ие изменится зпяк частотной рясстройки.

Однако при слсдукпцем появ1clli3II двух пмIll л ьсов 1! а Входе 9 В и ! О1)В3 Ic межд>113>мя импульсами iia входе 10 срабатывает блок

7 опознавания последоватслыкостп импульсов, 10 ко i op 1>ill Выдает короткиЙ им пу I bc Ilpll co13liaде»пи импульса на входе 9 с отрицательным импульсом на втором выходе основного триггера 1. Импульс блока 7 опознавания последовательности импульсов опрокидывает до15 полиительный триггер 6, и ключ 4 закрывается. Одновременно высокий потенциал на прямом выходе дополнительного триггера 6 открывает ключ 5. На выход 12 при этом проходит сигнал с выхода основного триггера 2, а

20 на выходе 11 папряжение cTalloi3I

Г1редлохкеииый цифровой 1acTQTIIQ-фазовый детектор по сравнению с известным имеет больший уровень выходного сигнала.

Формула изобретения

Цифровой частотно-фазовый детектор, содержащий два основных триггера, первые выходы которых подключены ко входам узла

35 сброса, выход которого соединен с первыми входами основных триггеров, о т л и ч а юшийся тем, что, с целью увели !сипя уровня

Выходного сигнала, введены два ключа, дополнительный триггер и два блока опозпа40 г33и!3л последовательности импульсов, первые

Входы которых соединены со Вторымп входамп осиови1,1х три!.героя, а В1.!ход!,! дополнительпого триггера подключены к управляющим входам ключей, ипформацпо!!ные входы

45 которых соединены со вторыми вы#одами осI I O I3 I »>I X r P I i r re P O I3 i I 13 TO P l>I M I I ВХОДамИ О Л 0 КО В опозпаваиия последоватслы!ости импульсов, Выходы которых подключены ко входам допо 11»ITcëi>iioão триггера.

Источники информации, принятые во внимание прп экспертизе

1. Патент СШЛ ¹ 3469198, кл, 329 — 50, 55 1969, 574864

Составитель Г. Серова

Тсхред И. Михайлова

Редактор Е. Дайч

Корректор Л. Орлова

Тппогпа<1п!я, пр. Сапунова, 2

Заказ 2212/17 Изд. М 766 Тира>к 818 Г1от,писное

НПО Государственного когпитета Совета Министров СССР по делана изобретений и открытий

1!3035, Москва, )К-35, Раугиская II;!6.,;!. 1, 5