Устройство для многоканального сопряжения телеграфных каналов с электронно-вычислительной машиной

Иллюстрации

Показать всеРеферат

Союз Советских

Соцл1алмстнческих

Республик (j ) ) 7 .э 6 4 2 (61)дополнительное к авт. свнд-ву (22) Заявлено Э0.06.75 (21) 2i 82276/24 с присоединением заявки № (23) Приоритет (43) Опубликовано05.10,77,Ьюллетень № 37 (46) 11ата опубликования описания 2g,i 0. 77 2 (51) М. Кл.

C 06 F 810

Государственный номатет

Совета Мнлнстроа СИр по делам нзаоретеннй

N 0TIIPbITIIH (53) УДК 68l..325 (088.8) E В. Валь и Г. Н, Машкин (У2) Авторы изобретения (71) Заявитель (54) УСТРОЙСТВО ДЛЯ МНОГОКАНАЛЬНОГО СОПРЯЖЕНИЯ ТЕЛЕГРАФНЫХ

КАНАЛОВ ЭЛЕКТРОННО-ВЫЧИСЛИТЕЛЬНОЙ МАШИНОЙ

Изобретение относится к области сбора и обработки дискретной информации и может быть испопьзовано в системах связи ЭВМ с телеграфными каналами, работающими с .переменной скоростью. 5

Известны устройства сопряжения ЭВМ с тепеграфными каналами(1), содержащие схему анализа состояний, бпока согпасования, бпока приоритета и блока запроса и выпопняющие сопряжение отдельных и совокупности телеграфных канапов, работающих с неизменной скоростью.

Такое устройство не может работать с группой каналов, работающих с разпичными скоростя ми. 15

Наиболее близким по технической сущности к изобретению явпяется устройство 12) дпя

cB5I3Ii ЭВМ с разнотипны ми каналами передачи данных, содержащее бпок согласования с канапами и два приемных блока. В1 1ходы 20 последних соответственно соадинепы со входами порогового блока, который связан цвусторонней связью с бпоком измерения обшей загрузки низкоскоростных каналов, выходом поцк IIoчанного к первому входу элемента 25

ИЛИ. Выход порогового элемента соединен со вторым входом эпаманта ИЛИ, выход которого соединен с выходом устройс-- ва.

Недостатком этого устройства яи яются низкая пропускная способность устройства, вследствии Отсутств1ья учета текущего состояния очереди на ввод в ЭВМ. ааль изобретения состоит в повышении пропускной способности устройства.

Эта цель достигается тем, что предложенное устройство содержит группу разделителей передачи по типу, вход каждого из которых соединен с соответствующим выходом бпока согпасования с каналами„

Первые, вторые и третьи выходы каждого разде11итепя передачи пО типу ПОдкпючены соответственно ко входам двух приемных бпоков и бпоку измерения общей загрузки низкоскоростных каналов.

Крома того, разделитель передачи по типу содержит буферный запоминающий блок, блок определения вида коца, бпок определения корости передачи, коммутатор, решаюшин

ЗпОк, блОк Опредепания границ ОООбше11ия „ счетчик базы анапиза, два триггера и дь»

575642 элемента И. П: рвые входы триггеров соединены со входом счетчика базы анализа, третьим выходом раздепителя и первым выходом блока определения границ, вход которого подключен ко входу раздепитепя и первым входам элементов И. Выход первого элемента И связан с первым входом буферного запоминающего блока, выход которого подключен к первому входу кдммутатора, выход которого соединен с первым выходом разделителя. Выход первого триггера соединен со вторыми входами первого эпемента И и буферного запоминающего блока, третий вход которого соединен с выходом решающе го блока, Второй выход бпока определения границ сообщения связан со вторым входом первого триггера.

Выход счетчика базы анализа соединен со вторым входом второго триггера и первым входом решающего блока, второй и третий входы которого соединены соответственно с выходами блока определения вида кода и блока определения скорости передачи, входы которых подключены к выходу второго элемента И, связанного вторым входом с выходом второго триггера. Выход решающего блока соединен со вторым входом коммутаторов, второй выход которого подключен ко второму выходу раздепитепя„

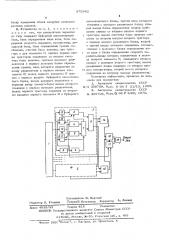

На чертеже представлена блок-схема устройства, Оно содержит блок согласования с каналами 1, разделители передачи по типу .2, включающие буферный запоминающий блок (БЗУ) 3, бпок определения вида кода 4, блок определения скорости передачи 5,коммутатор 6, решающий блок 7, блок опредепения границ сообшения 8, счетчик базы анализа 9, триггеры 10 и 11 и элементы

И 12 и 13. Кроме того, устройство содержит приемные блоки 14 и 15, пороговый блок 16, бпок измерения обшей загрузки низкоскоростных канапов 17. и элемент

ИЛИ 18.

Устройство работает следующим образом, При поступлении информации от блока

1 на разделитель 2 блок 8 выявляет начало сообщения и запускает счетчик 9, после чего выдает сигнал в блок 17, который измеряет обшую нагрузку каналов, работающих с низкой скоростью. При этом триггеры 10, 11 устанавливаются в единичное состояние, открывая элементы И ° 12 и 13.

Кроме того, сигнал с выхода триггера

10 переводит БЗУ 3 в режим запись".

Информация через элемент И 12 поступает в БЗУ 3, а через элемент И 13 на вход блоков 4 и 5, в которых производится соОтBeTcтвующий анализ.

При переполнении счетчика 9 триггер

11 опрокидывается, закрывая поступпение информации через элемент И 13 в блоки

4 и 5, Одновременно сигналом на первом входе запускается решающий блок 7, определяющий группу каналов, к которой принадпежит поступившее, сообщение, и формирующий сигнал переключения БЗУ 3 в режим запись-считывание и сигнал управления коммутатором 6. В зависимости от решения блока 7, сообщение через коммутатор из блока 3 считывается в блок 14 (первая группа каналов) или блок 15 (вторая группа каналов). На выходе одного из этих блоков формируется сигнал готовности, поступающий в блок 16, где содержимое порогового счетчика увепичивается на единицу. По достижении показаний этого счетчика заданного порога очередной сигнал

2о готовности проходит на элемент ИДИ 1 8, на выходе которого формируется сигнал запроса в ЭВМ. Если с канала второй группы приходит сигнал "начало сообщения, то сигналом из бпока 17 сбрасывается по?5 роговый блок 16 и выдается сигнал залроса в ЭВМ. При выявлении "конца сообшения в блоке 8 вырабатывается сигнал на перевод триггера 10 в нулевое состояние. При этом запирается элемент И 12, и БЗУ 3 перехоЗО дит в режим "считывание".

Таким образом, устройство позволяет адаптировать выдачу сигналов прерывания

ЭВМ в соответствии со скоростью принимаемой информации и увеличить пропускную

35 способность устройство.

Фор мул а изобретения

1, Устройство дпя многоканального со10 пряжения телеграфных каналов с ЭВМ, со держашее блок согласования с каналами, два приемных блока, выходы которых соответственно соединены со входами порогового блока, который связан двусторонней связью

45 с бпоком измерения обшей загрузки низко скоростных каналов, выход которого подключен к первому входу элемента ИЛИ, выход порогового элемента соединен со вторым входом элемента ИЛИ, выход которого

5О соединен с выходом устройства, о т и и— ч аю шее ся тем, что, сцельюувепичения пропускной способности устройства при работе каналов с переменной скоростью передачи, оно содержит группу раздепите55 пей передачи по типу, вход каждого из которых соединен с соответствуюшим.выхо- дом блока согласования с каналами, первые, вторые и третьи выходы каждого раздепигеля передачи по типу подключены соответственно ко входам двух приемных блоков и

575642 пирос

ИМ

Составитель В. Вертлиб

Редактор Л. Утехина ТехредВ, Куприянов Корректор А. Лакнда

Заказ 4035/33 Техред 818 Подписное

llHHHl iH Государственного комитета Совета Министров СССР по делам изобретений и открытий

1 1 3035, Москва, Ж-35, Раушская наб., д. 4/5

Филлип ППП Патент, г, Ужгород, ул. Проектная, 4 блоку измерения обшей загрузки низкоскоростных каналов.

2. Устройство по и. 1, о т л и ч а ю ш е е с я тем, что разделитель передачи по типу содержит буферный запоминающий блок, блок определения вида кода, блок опредения скорости передачи, коммутатор, решающий блок, блок определения границ сообщения, счетчик базы анализа, два триггера и два элемента И, причем первые входы триггеров соединены со входом счетI чика базы анализа, третьим выходом разделителя и первым выходом блока определения границ, вход которого подключен ко входу разделителя и первым входам элементов И; выход первого элемента И связан с первым входом буферного запоминаю1цего блока, выход которого подключен и

Первому входу коммутатора," выход которого соединен с первым выходом разделителя, Выход первого триггера соединен со вторыми входами первого элемента И и буферного запоминающего блока, третий вход которого соединен с выходом решающего блока; второй выход блока определения границ сообшения связан со вторым входом первого триггера; выход счетчика базы анализа соединен со вторым входом второго триггера и первым входом решающего блока, второй и третий входы которого соединены соответ-твенно с выходами блока определения вида кода и блока определения скорости передачи, входы которых подключены к выходу второго элемента И, связанного вторым входом с выходом второго триггера; выход решающего блока соединен со вторым вхо15 дом коммутатора, второй выход которого подключен ко второму выходу разделителя.

Источники информации, принятые во внимание при экспертизе:

1. Авторское свидетельство СССР

20 % 3597 69, М.кл. Н 04 f 1 1/15, 1 969.

2. Авторское свидетельство СССР

365706, М.кл. Q 06 F 9/00, 1970.