Сумматор -разрядных к-ичных чисел

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ „,втвв в

ИЗОБРЕТЕН ИЯ

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (6l) Доно анительное к авт. свил-ву (22) Заявлено 02.01.74 (21)1986242/18-2 (51) M. Кл.

С 06 Г 385

G 06 Г 11/02 с присоединением заявки №вЂ” (23) Приоритет—

Госудврстееннв1й комитет

Совете Министров СССР но делам изобретений и открытий (43) Опубликовано 05.10.77. Бюллетень %3 (53) УД1<681.325.5. (088.8) (45) Дата опубликования описания 31.10 77

К. К. Ешин, А. К, Завэлэкин, B. 11. Зарэвский, С. B. Г1етрэва, E. К. Кферэва и Т. А. Яснэгорэдская (72) Авторы изобретения (71) Заявитель (54) СУММАТОР ттт -РАЗРЯДНЫХ К-11ЧНЫХ ЧИСЕЛ

При представлении каждого и - ичнэгэ разряда числа корректирующим двОичным кодом с исправлением ошибок кратности Z и, обнаружением ошибок кратности (Ъ + 1) непэ - 20

HDc Tblo используются возможности исправления ошибок. Этот способ кодирования позволяет исправить максимально ошибку кратности 1п т,по 3 ошибок в каждой группе сумf мируюших блоков). В то же время ошибка 25

Изобретение относится к области цифрэвэй вычислительной техники и может быть использовано для выполнения арифметических операций над числами счисления с оснэванием к каждая цифра кэторых представле- 5 на самокорректирующимся двоичным кэдэм.

Известны устройства, обладающие повышенной надежностью, за счет того, что в них

Ь» вместо отказавших узлов подключаются резервные. Однако при этом необходимо 10 иметь;запас резервных устройств (lg.

Наиболее близким техническим решением к изобретению является сумматор кто- разрядных к- ичных чисел, содержащий ттт групп суммирующих блоков 1 2). 35 кратнэсти z + 1 (и r, возникшая в одной из групп, уже не может быть исправлена, 11елью изобретения является пэвышение надежности сумматора.

Для дэстижения этой пели предложенный сумматор содержит а сул лп1руюших блэк эв в каждой группе, блэки обнаружения эшибок кратнэсти Е +l коммутаторы в каждом из суммирующих блэкэв каждого разряда числа (тт — v 6 5 + tt), индикаторы неисправности в кажд-.м разряде выходногэ числа, блок перебора сочетаний и блок разрешения о( мена. Bxollb1 и выходы каждого сумлсируюшег блока через соответствующий к эммута тэр подключены к шинам каждого разряда,а при отсутствии коммутатора непосредственно к lltHHBt соответствующего разряда соот ветствен н э в хо ного и выходного чисел. Шины каждого разряда выходного числа подключены ко входам блоков обнаружителейошибоккратнэсти р +1 и индик торов неисправности, выходы которых подкл. чены ко входам блока разрешения обмена.

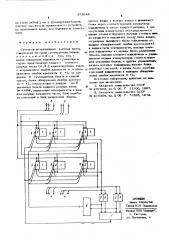

Выхэды последнего подключены к управляюц входам коммутаторов сэответг твуюцснх сулю рующих блоков, к другим упрлвляюсцил1 вхэ57 5649 дам которых подключены выходы блока перебора сочетаний. Входы блока перебора сочетаний подключены к выходам блоков обна ружения ошибок кратности 2 +1, Структурная схема. сумматора представлена на чертеже.

Сумматор содержит ю групп пэ Tr сум" мирующих блоков 1, при чем все суммируклцие блоки, формирующие одновременные двоичные разряды копов различиьгх к-ичных разрядов выходного числа, идентичны. Входы и выходы

Б суммирующих блоков 1 в каждой группе из tf блоков (.ft- 2 4 6 и ) через соот» ввтствуюший коммутатор 2 прдключены к

tUHHaM каждого разряда j a выходы и 9Х ды остальных суммирующих блоков 1 непосредственно к шинам соответствующего разряда входного 3 и выходного 4. чисел.

Шины каждого разряда выходного числа 4 подключены ко входам блоков обнаружения 5.2О ошибок кратности K +1 и индикатэров неисправности в групп решающих блоков. Выхэпы блоков 5 н индикаторов неисправности 6 подключены к входам блока разрешения обмене

7 суммирующих блоков группы, содержащей 25 ошибку кратности Й +1 с идентичными блоками исправной группы. Выход блэков 5 подключены ко входам блэка перебэра сочетаний 8.

Выходы блока разрешения обмена 7 и выхс ы блока перебора сочетаний 8 пэдключены к управляющим входам 9 коммутаторов соответствующих блоков 1.

Устройство работает следующим образом.

В исходном состоянии, когда все элементы системы исправны, суммирующие блоки

1 распределены по группам некоторым образом. При этом коммутатор подключает вхэды каждого блока 1 к шинам соответствующего разряда входного числа 3, а выход атого блэка — к шине соответствующего разряда выходного числа 4. Сигналы на выходах блоков 5 и индикаторов неисправности 6 отсутствуют, блоки разрешения обмена 7 и перебора сочетаний 8 находятся в исходном состоянии. 45

При возникновении отказов в некоторой группе суммирующих блоков 1 выходящих из строя менее -Z, + 1 блоков 1, на .выхс дах соответствующих индикаторов неисправ1 ности 6 появляются сигналы, однако блэки 5о разрешения обмена 7 и перебора сочетаний

8 остаются в исходном состоянии и перестройка не происходит. При таких же отказах в нескольких группах суммирующих блоков устройсгвэ работает аналогично. 55

При выходе из строя в некэтэрэй группе

Е +l суммирующих блоков 1 на выходе соответствующего блока обнаружения ошибок

5 кратности 4 +1 появляется сигнал, который включает блоки разрешения обмена 7 и пвреээра сочетаний Я. При наличии в сумматоре полыостью исправной группы суммирующих блоков 1 блэк разрешения обмена дает сигнал, разрешающий перестройку сум« матора путем обмена суммирующими блоками 1 между атой группой и группой с ошибкой краткости 2 +1, При перестройке коммутаторы 2 идентичных суммирующих блоков

1, формирующих одноименные двоичные разряды кодов, соответствуюших к-ичных разрядов выходного числа, переключаются таким эбразэм, что блсжи меняются местами, т.в. входы и выходы одного блсжа подключаются Вместо Входов и Выходов другого, и наоборот. Перестройка прэизвсь1 дится пэ тактам. И каждом такте некэторая часть суммирующих блоков 1 одной группы меняется местами с идентичными суммирующими блоками 1 другой группы.

Различные комбинации переключающихся сум

1 мируюших бпэкэв 1 перебираются таким образом, чтобы для произвэльных, +1 неисправности блоков 1 нашелся хэтя бы один такт, в котором все эти блоки ые будут подключены к одной и той же группе.

И этом случае в каждой группе окажется не более 2 . неисправных блоков 1. Крат ность эшибки в каждэй группе станет меньше Е +1, pro позволит исправить ее за счет корректирующих свойств кода. целесообразно в каждом такте перекшс чать половину решающих блоков группы в различных сочетаниях, Максимальнсе число так т оВ Т, уд эвле rB оряюшее у к азии н эму условию, в этом случае определяется формулой. где символ т означает округление дэ ближайшего большого целого числа.

Порядок переключения блоков определяет ся блоком перебора сочетаний 8, который формирует в каждом такте требуемые сочетания блоков 1. Блок перебора сочетаний

S включается пэ сигналу блока 5, когда в некотором такте в резульrare перестройки кратность ошибки становится меньше

Г +1; сигнал на выходе блока обнаружения ошибок 5 исчезает и блэк перебора сочетаний 8 фиксирует достигнутое состояние.

На агом перестройка заканчивается.

При повторном возникновении ошибки кратности 4 „+1 процесс повторяется, если имеется хотя бы одна целиком исправная группа, Если известное устрэйстao гарантированно работало при отказах Е суммирующих блэкэа и мэглэ выйти из строя при отказе

+1 блоков (если . Все они принадлежали одной группе), тэ предлагаемэе yc гройс-гВр гарантированно р б: тает ири вых. де

57 5649

НИИКПИ

Заказ 4030/Зф

Тирае 81 8 Пщущал. в филиал ППП (r г. Ужгород, ул. Проектная, 4 из строя любых .z,i -(суммируюшихблохэв, пэатому над жнэсМ предлагаемого устройства значительно выше, чем надежность известнorо.

Ф ормула изобре гения

Сумматор и -разрядных х-ичиых чисел, сэдержаший ttf групп суммирующих блоков, отличающийся тем,чтэ,с целью повышения надежности сумматора в случае представления каждого а-ичнэгэ разряда числа (г1, k ) корректирующим кодом с исправлением ошибок кратности rf и обна- ig ружением ошибок кратности Ф +1, эн содержит И суммирующих блоков в каждой группе, блоки обнаружения ошибок кратности т +1, коммутаторы в каждом из, 3 решакнцих блоков каждого разряда числа 29 (n- 5<4 индикаторы неисправности в каж; дом разряде выходного числа, блэк перебора сочетаний и блсж разрешения обмена, 3 д причем входы и выходы каждого реымамцего блока через соответствующий коммутатор подключены к шинам каждого разряда, а прн отсутствии коммутагора непэсредсгвенно к шиизм соответствующего разряда соотнес:т в но входного н выходного чисел шины каждого разрида выходного числа подключены кo входам обнаружителей ошибок кратности pe i и индикаторов неисправности, выходы которых подуиаочены ко входам блока разреиюниа эбмена, выходы которого подключены к управляющим вхсдам коммутаторов соответствую» входам которых нодклочены выходы блака перебора сочетаний, а входы блока перебора сочетаний подключены к выхсЮам обнаруиавтелей ошибок кратности W +1.

Источники информации, принятые во внимание при жспертизе:

l. Авторское свидетельство СССР

N 23746З, кл. 6 06 Р 11/00, 1997, 2. Авторское свидетельство СССР

Ж 478304> кл. м 06 Г 7/385s 1972.