Ассоциативное запоминающее устройство

Иллюстрации

Показать всеРеферат

t (1ц 576608

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К ЛатОРСКОМУ СВИДИТЫЬСТВУ

Союз Советских

Социалистических

Республик

;х ф Ф (61) Дополнительное к авт. свид-ву (22) Заявлено 13.02.75 (21) 2104774/24 с пр tcoct!itic;itteit заявки № (23) Приоритет (43) Опубликовано 15.10.77. Вюллетень ¹ 38 (45) Дата опуo tt tioDtt II titi oti t ten li il5I 1- . 1 О. / ( (51) 1. 1 л. - б 11С 15, 00

Государственный комитет

Совета Министров СССР по делам изобретений и открытий (53) УД1 681.327(088.8) (72) Авторы изобретения Г. В. Виталиев, А. Д. Гвинепадзе, Р. В. Смирнов и Г. Д. Софийский (71) Заявитель (54) АССОЦИАТИВНОЕ ЗАПОМИНА1ОЩЕЕ УСТРОЙСТВО

Известно ассоциативное запоминающее устройство, содержащее дешпфраторы опроса, входы которых соединены с выходами соответствующих регистров опроса, а выходы— с адресными шинами адресных запоминающих блоков, одноименные разрядные шины которых подключены к соответствующим детекторам. В известном устройстве избыточность прп реализации ассоциативного поиска на адресных элсме ITBx быстро возрастает с увеличением числа адресных шин запоминающих блоков, т. е. с увеличением их информационной емкости.

Цель изобретения состоит в упрощении устройства. В описываемом устройстве это достигается тем, что оно содержит дополнительные регистр опроса и дешифратор опроса, выходы которого подключены к управляющим входам соответствующих детекторов, а входы — к выходам дополнительного регистра опроса, соединенным с управляющими входами других дешифраторов опроса.

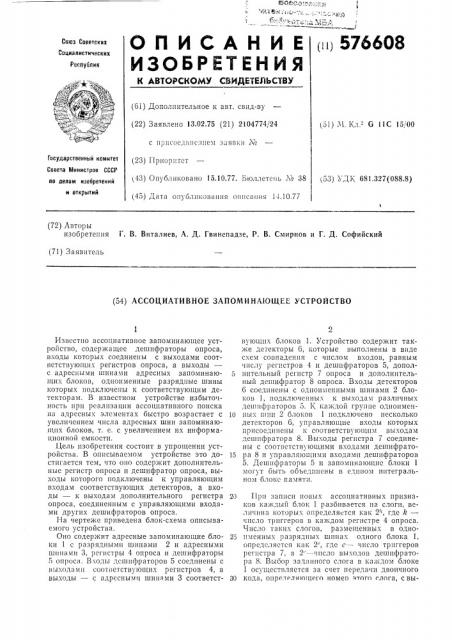

На чертеже приведена блок-схема описываемого устройства, Оно содержит адресные запоминающие блоки 1 с разрядными шинами 2 и адресными шинами 3, регистры 4 опроса и дешифраторы

5 опроса. Входы дсшифраторов 5 соединены с выходами соответствующих регистров 4, а выходы — с адресными шинами 3 соответствующпх блоков 1. Устройство содержит также детекторы 6, которые выполнены в виде схем совпадения с числом входов, равным числу регистров 4 и дешпфраторов 5, допол5 нптельный регистр 7 опроса и дополнительный дешифратор 8 опроса, Входы детекторов

6 соединены с одноименными шинамп 2 блоков 1, подкл оченных к выходам различных дешпфраторов 5. 1 каждой группе одноимен1о ных шпн 2 блоков 1 подключено несколько детекторов 6, управляющие входы которых присоединены к соответствующим выходам дешифратора 8. Выходы регистра 7 соединены с соответствующими входами депгифрато15 ра 8 и управляющими входами дешпфраторов

5. Дешифраторы 5 и запоминающие блоки 1 могут быть объединены в едином интегральном блоке памяти.

2Э Ilp;I записи новы.; ассоциативных признаков каясдый блок 1 разбивается на слоги, Величина которых Определяется как 2", где k— кисло триггеров в каждом регистре 4 опроса.

Число 1àêèõ слогов, размещенных в одно25 именных разрядаых шинах одного блока 1, определяется как 2, где e — число триггеров регистра 7, а 2 — число выходов дешифратора 8. Выоор заданного слога В каждом блоке

1 осущсствляется за счет передачи двоичного

30 кода, опрел лякнпего номеп этого rëoãà, свы576608

4 ходов регистра 7 на управляющие входы соответствующего дешифратора 5.

1(од, поступающий на вход одного из регистров 4, передается на входы соответствующего дешифратора 5. Одновременно на управляющие входы этого дешифратора поступает код с выходов регистра 7. При этом возбуждаются одноименные адресные шины 3 устройства, номер которых определяется двоичным кодом на входе дешифратора 5. Кроме того, возбу)кдаются одноименные разрядные шины 2, соединенные со входами этого детектора. Все запоминающие элементы блоков 1, соединенные с этими шинами 2, предварительно дол)кны оыть установлены в одно состояние, например «логический 0» или «логическая 1». В запоминающий элемент, расположенный на пересечении выбранных адресной и разрядной шин данного блока 1> записывается «логигеская 1» пли «логический О», т. е. запоминается номер возбужденного выхода дешпфратора 5 опроса. Ассоциативное слово из пг слогов IIQ !г разрядов записывается на

«озбужденных разрядных шинах 2 путем запоминания состояний всех дешпфраторов 5.

Другое ассоциативное слово может быть записано па тех же разрядных шинах 2 при пзмспепип кода, . ранящсгося в дополнительном регистре 7 опроса. При этом «едпппчныс» или

«нулевые» метки, относящиеся к другим словам этих шпн, сохраняются, так как выборка в полупроводниковых блoкаx памяти осуществляется без разрушения информации.

При опросе в соответствии с кодами íà регистрах 4 и 7 возбу)кдаются одноименные адресныс шины 3. Наличие «логической 1» или

«логического 0» па соответствующей разрядной шп с 2 блока 1 свидетельствует о совпадсшш кода па одноименном регистре 4 с кодом ассоцпап!вного слога, записанного вэтом блоке. Появ10HIIC на соответствующей шине

2 «логического 0» илп «логической 1» являстС51 ПРПЗП аl<ОМ 11ССОВПЗДС!1ИЯ > 1<331111111>IХ КОДОВ.

Если происходит полное совпадение данного ассоциативного слова с кодами па всех регистр3х 4, то на входах соответствующей группы детекторов 6 появляется ровно m сигналов

5 совпадения, а выбранный детектор 6 в этой группе определяется с помощью дешифратора 8.

Устройство может быть использовано в двух ре)кимах. Если дополнительные код оп-!

О роса заранее известен, то этот код заносится па регистр 7, и опрос вссго массива памяти производится за одно обращение. Для полно о просмотра массива памяти требуется 2 обращений, где l — разрядность дополнительного

)5 кода опроса, при этом регистр 7 должен быть в режиме счет>!ика. Во втором жиме опрос является смешанным адресно-ассоциативным. Однако общее время поиска в этом режиме возрастает на вели ишу мсш,ше, 2!1 чем 2, так как скорость переключения регистра 7 определяется временем выборки блоков

1, которос для реальных микросхем памяти составляет примерно q времени цикла. В пер«ом режиме поиск осуществляется за время

23 одного цикла обращения к одному блоку 1.

Ф О Р м >, 3 II 3 0 О P e 1 е 1111 и

Ассоциативное запоминающее устройст«о, 30 содержащее дешифраторы опроса, входы которых соединены с выходамп соответствующих регистров опроса, а выходы — с адресными шинами адресных запоминающих блоков, одноименные разрядные шины которых

35 подключены I< соответствующим детектора м, о тл и ч а ю щ е е с я тем, ITQ, с целью упрощсIlII5I 1 С! рОЙСТ«а, ОПО СО Iep)!пые регистр опроса и дешифратор опроса, выХОДЫ КОТОРОГО ПОДК;!!O>!el!1>I I< УПР3«ЛЯIОП(И vl

-!.") «. одам соответствующих детекторов, а входы --- к выходам дополнительного регистра опроса, со<дипепным с управляющими «ходамп других дешифраторов опроса.

57G608

Составитель В. Рудаков

Техред И. Михайлова

Редактор Л. Тюрина

Корректор Л. 0pлова

Подписное

Типография, пр. Сапунова, 2

Заказ 2306/ll Ивд. ЛЪ 820 Тираж 738

1-1ПО Государственного когиитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, )Y,— 35, Раугиская иаб., д. 4/5