Устройство для формирования синхросигнала

Иллюстрации

Показать всеРеферат

О П И C А H И Е i!i) 57667О

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (б1) Дополнительное к авт. свид-ву (22) Заявлено 29.12.75 (21) 2305061/09 с присоединением заявки ¹ (23) Приоритст (43) Опубликовано 15.10.77. Бюллетень № 38 (45) Дата опубликования описания 20.10.77 (51) М. Кл."- Н 04L 7/08

Государственный комитет

Совета Министров ССОР оо делам изобретений и открытий (53) УДК 621.394.662 (088.8) (72) Авторы изобретения Л. А. Зак, 1О. И. Митропольский, В. С. Новизснцев, В. A. Отто и А. А. Соколов (71) Заявитель (54) УСТРОЙСГВО ДЛЯ ФОРМИРОВАН И 1 СИНХРОСИГИАЛА

Изобретение относится к области вычислительной техники и может быть использовано в системах, объединяющих устройства, различающиеся по скорости выдачи и приема данных, находящиеся на значительном расстоянии друг от друга.

Известно устройство для формирования синхросигнала, содержащее усилитель приема ответного сигнала и блок выделения синхросигналов, к входу которого подключен выход триггера блокировки через элемент И (1)

Однако известное устройство не обладает достаточным быстродействием, вследствие применения в нем старт-стопного метода синхронизации обмена между передающим и приемным устройствами, при котором интервал между последовательными сообщениями не может быть меньше двойного времени распространения сигнала по линии.

Для повышения быстродействия в предлагаемое устройство для формирования синхросигнала, содержащее усилитель приема ответного сигнала и блок выделения синхросигналов, к входу которого подключен выход триггера блокировки через элемент И, введены реверсивный счетчик, блок сравнения и регистр, при этом к входам блока сравнения подключены соответственно выходы реверсивного счетчика и регистра, а вы .од блока сравнения подключен к единичному входу триггера блокировки, к нулевому входу которого подключен выход усилителя приема ответного сигнала и вход «Вычитание» реверсивного счетчика, к входу «Суммирование» которого подключен выход блока выделения синхросигналов.

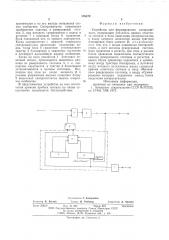

На чертеже представлена структурная электрическая схема описываемого устройства, содержащего усилитель 1 приема ответного сигнала и блок 2 выделения синхросигналов, к входу которого подключен выход триггера 3 блокировки через элемент 4 И, реверсивный счетчик 5, блок б сравнения и регистр

15 7, при этом к входам блока б сравнения подключены соответственно выходы реверсивного счетчика 5 и регистра 7, а выход блока б сравнения подключен к единичному входу триггера 3 блокировки, к нулевому входу ко20 торого подключены выход усилителя 1 приема ответного сигнала и вход «Вычитание» реверсивного счетчика 5, к входу «Суммирование» которого подключен выход блока 2 выделения спнхроспгна10B.

25 Устройство раоотаст следующим образом.

Прп готовности сообщения сигнал поступает на вход элемента 4 И, на втором входе которого установлено разрешение, т. е. триггер

3 блокировки находится в нулевом состоянии.

30 При этом запускается блок 2 выделения сино76670! ! ! ! ! ! ! !

Составитель Г. Захарченко

Тсхрсд H. Рыбкина

1(оррсктор Л. Орлова

Редактор В. Баглай

Подписное

Заказ 2293, 9 Изд. М 822 Тираж 818

НПО Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Я(-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2 хросигналов и на его выходе появляется сигнал сообщения. Синхроимпульс производит прибавление единицы в реверсивный счетчик 5, код которого сравнивается с кодом в регистре 7 с помощью блока 6 сравнения.

Если совпадения нет, то процесс повторяется.

Когда одновременно с выдачей очередного синхроимпульса происходит совпадение кодов, тогда блок 6 сравнения устанавливает триггер 3 блокировки в единичное состояние и блокирует дальнейшую выдачу сообщения.

Когда на вход усилителя 1 поступает ответный сигнал, производится вычитание единицы из реверсивного счетчика 5, т. е. совпадение нарушается, и триггер 3 блокировки устанавливается в нулевое состояние. Возникшее при этом на входе элемента И 4 условие разрешения выдачи позволяет блоку

2 выделения синхросигналов выдать очередное сообщение.

В предложенном устройстве за счет исключения времени пробега сигнала по линии существенно повышается быстродействие.

Формула изобретения

Устройство для формирования синхросиг. нала, содержащее усилитель приема ответного сигнала и блок выделения синхросигналов, к входу которого подключен выход триггера блокировки через элемент И, о т л и ч а ю щ ее с я тем, что, с целью повышения быстродействия, в него введены реверсивный счетчик, 10 блок сравнения и регистр, при этом к входам блока сравнения подключены соответственно выходы реверсивного счетчика и регистра, а выход блока сравнения подключен к единичному входу триггера блокировки, к нулевому

15 входу которого подключены выход усилителя приема ответного сигнала и вход «Вычитание» реверсивного счетчика, к входу «Суммирование» которого подключен выход блока выделения синхросигналов.

20 Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 372723, кл. Н 041 7/08, 1973.