Преобразователь двоичного кода смешанных чисел в двоично- десятичный код

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОВаИтИНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистиыеских

Республик (111 577524 (61) Дополнительное к авт. свид-ву (22) Заявлено 09.0 1.75 (21) 2096546/24 с присоединением заявки № (23) Приоритет

2 (51) М. Кл.

q 06 F 5!02

Гооудврствеииый комитет

Соввтв Мииистров СССР

ll0 делам иэооретеиий и открытий (43) Опубликовано 25.10.77. Бюллетень №89 (У) УД1(681.325 (088.8) (45) Дата опубликования описания 10.11.77 (72) Авторы изобретения

В, Н, Розов и В. В, Чеклин (71) Заявитель (54) ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНОГО KOLA СМЕШАННЫХ

ЧИСЕЛ В ДВОИЧНО-ДЕСЯТИЧНЫЙ КОД

Изобретение относится к области вычислигельной техники и автоматики и может быть использовано в специализированных арифметических и логических устройствах, оперирующих в двоичной системе счисления и выдающих результат обработки информации для восприятия в десятичной системе.

Известен преобразователь кодов 1 из двоично-десятичной системы счисления в двоичную, содержащий блок управления, переклю- 10 чатель экивалентов, запоминающее устрой1 ство двоичных. эквивалеитов, распределитель двоичных разрядов по весам, регистр числа, одноразрядный двоичный сумматор, регистр результата (1) . Быстродействие 15 этого преобразователя недостаточно высоко и зависит от числа двоичных разрядов тт; преобразование К вЂ” разрядного десятичного числа длится в течение времени 4)» q$ где -длительность одного такта пре- 20 образования.

Из известных преобразователей двоичного кода в двоично-десятичный наиболее близким по технической сущности к заявленному является преобразователь двоичного кода смешанных чисел в двоично-десятичный код, содержащий блок управления, вход котот. Гот соединен с входной управляющей шиной,}выход — c первым входом блока формирования

=игналов,: первый выход которого соединен через переключатель эквивалентов с входом запоминающего блока (2) . Схема этого преобразователя весьма проста, а перевод двоичного кода смешанных чисел в двоичнодесятичный код осуществляется беспрограммным путем с использованием двоичных эквивалентов десятичных чисел вида (1д ) е где )(-0,1,2,3......Однако быстродейст вие данного преобразователя также зависит от числа двоичных разрядов тт, а время перевода достигает значения 9),тт i .

Целью изобретения является повьппение быстродействия преобразования двоичного кода смешанных чисел в двоично-десятичный код.

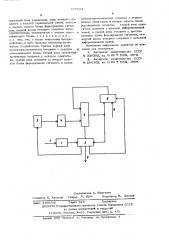

Это достигается тем, что в преобразователь введены сумматор-вычитатель и сдвигатель, причем первый вход сумматора>вычитателя соединен с выходом запоминаю1щего блока, второй вход сумматора-вычига577524 теля соединен с выходом сдвигателя, третий вход соединен со вторым выходом блока формирования сигналов, а выход сумматора - вычитатепя соединен с первым входом сдвигателя и вторым входом блока формирования сигналов, второй вход сдвигателя соединен с входной информационной шиной, а третий вход соединен с третьим выходом блока формирования сигналов, четвертый выход которого соединен с выходной информационной шиной, На чертеже представлена структурная схема преобразователя двоичного кода смешанных чисел в двоично-десятичный код.

Преобразователь двоичного кода сме- 15 шанных чисел в двоично-десятичный код содержит блок управления 1, блок 2 формирования сигналов, переключатель эквивалентов 3, запоминающий блок 4, сумматор-вычитатель 5, сдвигатель 6, входную управляю- 20 шую шину 7, входную инфорллационную шину 8, выходную информационную шину 9, Преобразование осушествляется последовательным нахождением тетрад двоично-десятичного кода смешанных чисел, начиная со старшей тетрады, методом деления обрабатываемого двоичного параллельного кода без ,ace=.åновления остатка на двоичные,эквиваленты десятичных чисел вида (10 2 ), где — число десятичных разрядов пер 30 лой !асти переводимого числа; f.(i=1,2,3, ° ..

<4 -1), k, k — обшее число десятичных разрядов переводимого числа.

Преобразователь работает следую цил1 образом„Управляю ций импульс, поступаюший по шине 7, запускает блок управления

1, который вырабатывает импульсы, необходимые для автономного функционирования преобразователя, и пересылает их в блок 2 формирования сигналов. Сигнал с выхода блока 2 переводит переключатель эквивалентов 3 на считывание из запоминающего блока 4 соответствую>пего эквивалента десяти ных чисел (в начале преобразования— старшего, то есть при ?И=1), двоичный па»раллельный код которого йоступает на вход сумматора-вычитателя 5 и служит при на— хождении данной тетрады делителем. Одновременно на другой вхоц сумматора»вычитаi0 теля 5 в первом такте преобразования подается через сдвигатель 6, управляемый блоком 2, двоичный параллельный код входной информации, который берется делимым (в дальнейшем,4 делимым является предыдуший остаток}. Блок 2 разрешает в первом такте преобразования вычитание делителя из делимого в сумматоре-вычитателе 5, откуда на вход, сдвигателя 6 . поступает код полученного частичного остатка, знаковый разряд которого поступает также в блок 2 для фор- 60 мирования кода двоично-десятичной тетрады и определения необходимости вычитания или сложения B следующем такте преобразования, При этом, если по анализу знакового разряда сумматора-вычитателя 5 частичный остаток оказался отрицательным, то блок

2 выдает на выходную информационную шину

9 в виде очередной цифг.- двоично-десятичной тетрады-нуль и noni отавпивает в сумматоре-вычитателе 5 пепи сложения для следуюшего такта преобразования, а если частичный остаток получился положительным, то на выходную информационну:> шину

9 выдается единица, а в следуюшем такте производится вычитание делителя из делимого. В следуюшпх тактах определения данной двои шо-десятичной тетрады делимое, т, е, предьшуший частичный остаток, передается через сдвигатель 6 на вход сумматора-вычитателя 5 со сдвиголл кода на один двоичный разряд в сторону старших разрядов, делитель остается прежним. После нахождения всех цифр двоично-десятичной тетрады, т, е. выполнения четырех тактов, в случае отрицательного остатка производится восстановление положительного остатка в дополнительном такте путем прибавления в сумматоре-вычитателе 5 того же делителя к отрицательному остатку. Для нахождения последуюших двоично-десятичIIbIx тетрад переключатель эквивалентов 3 переводится под воздействием сигналов блока

2 на выборку из запоминаюшего блока 4 следующих по-порядку (меньших по величине) эквивалентов, которые берутся новыми делителями, в качестве делимых берутся предыдушие положительные остатки и выполняется порядок вышеописанных действий определения кода каждой тетрады. Процесс преобразования будет повторяться до тех пор, пока не будут найдены все десятичные разряды числа, В описываемом преобразователе время перевода смешанных чисел из двоичного в двоично-десятичный код уменьшается до значения

5 Jj E Й не зависит от разрядности двоичного кода обрабатываемых чисел, что значительно повышает его быстродействие. При этом применение схемы предлагаемого преобразователя в арифметических и логических устройствах специализированных цифровых вычислительных машин позволяет использовать его узлы при выполнении других операций; формула изобретения

Преобразователь двоичного кода смешанEihIx чисел B пвоично-десятичный код, со577524

Составитель А. Шкатулла

Редактор Н. Хлудова Техред 4. Цупа Корректор М. Демчик

Заказ 4186/36 Тираж 818 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб„д. 4lS

Филиал ППП Патент" г. Ужгород, ул. Проектная, 4 шержаший блок управления, вход которого со.единен с входной управляющей шиной, выход с первым входом блока формирования сигна;лбв, первый выход которого соединен через переключатель эквивалентов с входом запоминаюшего блока, о т л и ч а ю ш и й— ,с я тем, что, с целью повышения быстродействия, в него введены сумматор-вычитатель и сдвигатель, причем первый вход сумматора-вычитателя соединен с выходом qp запоминаю пего блока, второй вход сумматоравычитателя соединен с выходом сдвигателя, третий вход соединен со вторым выхо- . дом блока формирования сигналов, а выход сумматора-вычитателя соединен с первым

BxoEIoM сдвигателя и вторым входом блока формирования сигналов, второй вход сдвиГателя соединен с входнойi информационной шиной, а третий вход соединен с третьим выходом блока формирования сигналов, четВертый выход которого соединен с выходной информационной шиной.

Источники информации, принятые во вниМание при экспертизе:

1. Авторскм свидетельство СССР

No 336382, кл. & 06 5 Gt02, 1972.

2. Ав торск ое свиде тельство СССР

No 296102, кл. С 06 P 5102, 1969.