Устройство для умножения частот

Иллюстрации

Показать всеРеферат

е.отоа т:оветсннн

Социалистические

Республик

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

111 577527 (61) Дополнительное к авт. синд-ву (22) Заявлено 20.10.75 (21) 21 83038/24 с прнсоедттненнем заявки ¹ (23) Г! риоритет

2 (51) М, Кл.

С 08 Р 7/3Гт

Государстеенный комитет

Сонате Министраа СССР по делам изобретений и открытий (43) Оттубликовано 25.10,77 Бюллетень №3, (53) УДК 881.325..57 (088.8) (45) Дата опубликования описания 11.11.77 (72) Лвтортн изобретении

b. В, Новоселов, Р, M. Трахтенберг,, В. A. Староверов и В. П. Ганас (71) Заявите,1ь (54) УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧАСТОТ

Изобретение относится к области автоматики и вычислительной техники и может быть использовано в устройствах, требую1liHx повышения частоты электрических сиг-! талОВ, 5

Известны устройства для умножения частот.

Один нз известных умножителей частоты 1 1) содержит импульсно-фазовый детектор, управляемый генератор и делитель частоты.

11ри достаточно высоких быстродействии и точности такой умножитель может рабо1 тать в узком диапазоне умножаемых частот. Для увеличения диапазона работы в умножитель вводится линейный преобразователь периода входной частоты в напряжение. Это однако приводит к сложности технической реалнзапии и настройки умножителя.

Другой из известных умножителей (2) 20 также содержит управляемый генератор и делитель частоты, B качестве фазового детектора в нем использован реверсивный счетчик, Фикснруютпим элементом является дешифратор код-нанряжение. Кроме того, умно- 25 житель включает интегратор, сумматор н цепь тактования на триггере. В таком устройстве обеспечивается расширение диапазона. умножаемых, частот, однако равномерность выходной части и быстродействие в нем низки. Умножитель отличается также сложностьто технической реализации.

Прототипом изобретения является устройство для умножения частот 13) содер3-- ) жашее триггеры, элементы Й, генератор управляемой частоты подключенный выт холом к выходу устройства и входу делителя частоты, соединенногз выходом с первым входом первого элемента И, второй вход которого подключен к первому входу второго элемента И и первому выхолу первого триггера, соединенного вторым выходом с первыми входами третьего и четвертого элементов И, причем второй вход третьего элемента И соединен с первым вьтходом второго триггера, подключенного т ервым вхолом к выходу первого элемента И, а первый вход третьего триггера соелинен с вхолом устройства.

577527

Такой умножитель, обеспечивая расширение частотного диапазона и повышение быстродействия, отличается сложностью технической реализации и недостаточной точностью

"умнойения частоты. Последнее вызвано тем что преобразование входной частоты умно жителя в цифровой код в любом случае сопровождается погрешностью, пропорциональной величине .дискретности заполняюшего tf -разрядные вычитаюшие счетчики сигнала. Вслед->О ствие этого выходная частота умножитепя не является линейцой функцией входной частоты.

Целью изобре "ения является упрощение

::устройства и .повышение точности умноже- 1 и ия б

Это достигается тем, что в устройство введены элементы задержки и интегратор, соединенный входами с выходами второго и третьего элементов И; а выход интегратора соединен с входом генератора управляемой частоты, причем второй вход второго элемента И подключен ко второму выходу второго триггера, соединенного вторым .вхо5 дом с выходом четвертого элемента И, вто- рой вход которого подключен к выходу третьего триггера, соединенного вторым входом с выходом устройства, и к входу первого элемента задержки, выход которого соединен с первым входом первого триггера, под-зо ключенного вторым входом через второй элемент задержки к выходу делителя частоты.

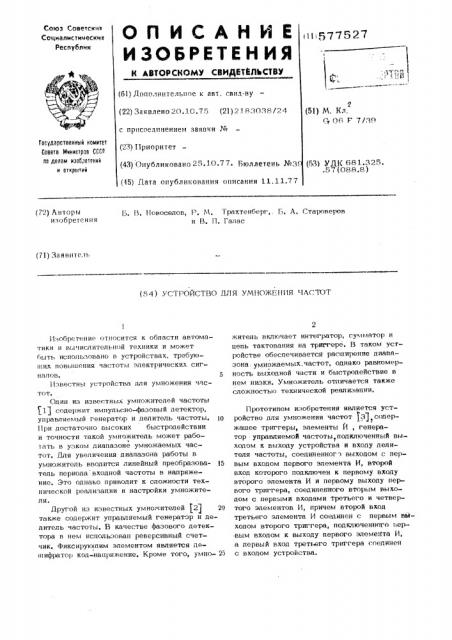

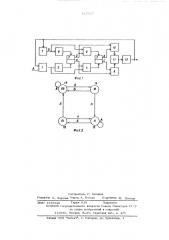

Иа фиг. 1 представлена блок-схема предлагаемого устройства; на фиг. 2 -направленный граф работы его элементов.

Устройство для умножения частот содержит две параллельные цепочки элементов, первая из которых включает последовательно соединенные триггер 1, элемент задержки

2, левое плечо триггера 3, элемент И 4, левое плечо триггера 5, элемент И 6. Вторая цепочка состоит из последовательно включенных делителя частоты 7, элемента задержки 8, правого плеча триггера 3, эле45 мента И 9, правого плеча триггера 5, элемента И 10. В каждой из цепочек входы элементов задержки 2 и 8 соединены с другими входами элементов И 4 и 9, соответственно выходы триггера 3 связаны с другими входами элементов И 6 и 10. Выходы элементов И 6 и 10 подключены к прямомуиинверсному входам интегратора 11, выход которого связан с генератором 12 управляемой частоты. Выход генератора 12:„ соединен с входами триггера 1 и делителя частоты 7.

Умножитель частотно-импульсных сигналов работает следующим образом. Предположим, чтс в исходном состоянии на. выходе а триггера 3 и на выходе с триггера

5 присутствуют нулевые потенциалы. Эт:.: состояния триггеров примем эа единичные на направленном графе (см. фиг.2), где в кружках через 1 и 0 обозначены состояния, соответственно, триггеров 3 и 5, а стрелками обозначены переходы из одного состояния в другое под действием отдельных импульсов А или B. Общее состояние схемы, когда оба триггера в нулевых состояниях обозначены цифрой 13. :С приходом импульса входного сигнала А цепь тактования на триггере 1 формирует импульс, синфаэный с импульсами генератора 12, Так как на элемент И 4 приходит сигнал запрета с триггера 3, то импульс с выхода триггера

1 не пропускается через промежуток времени на вход триггера 5.

Этот импульс через промежуток времени E сформированный элементом задержки 2, изменяет состояние триггера 3 ° На выходе этого триггера устанавливается нулевой потенциал. В таком состоянии импульс обратной связи с выхода делителя частоты 7 не проходит через элемент . И 9 на вход триггера 5. Однако через промежуток времени 1., сформированный элементом задержки 8, ой изменяет состояние триггера 3, подготавливая запрет входному импуцьсу на прохождение через элемент И 4, На направленном графе это соответствует переходу из состояния 13 в состояние 14.

Бремя задержки выбирается несколько больше временного промежутка t < этим са1r мым устраняется одновременный приход импульсов на оба входа триггера 3.

Таким образом, чередование входных импульсов и импульсов обратной связи приводит к перебросу триггера 3, причем состояние триггера 5 при этом не меняется (состояния 13 и 14) ° Приход подряд двух импульсов (например входных) приводит к такому состоянию, когда в момент появления на входе элемента И 4 импульсов с выхода триггера 1, на другом входе элемента И 4 прису тс твуе т разрешающий потенциал. В этом случае триггер 5 преобразовывается в единичное состояние. На направленном графе это соответствует переходу из 14 состояния в 15, Очевидно, что величина широтноимпульсного сигнала с выхода триггера 3, когда он переходит иэ состояния 13 в сoстояние.-. 14 и обратно, а также из состояния 15 в состояние 16 и обратно, пропорциональна фазовому рассогласованию между импульсами частот А и Б.

Триггер 5 перебрасывается с приходом двух подряд одноименных импульсов, т.е. изменением знака фазового рассогласования, С помошью элементов И 6 и 10 триггер 5 производит коммутацию широтно-имi 775 27 пульсных сигналов с выхода триггера 3 в состояниях 15 и 16 на прямой вход интегратора(.11 и в состояниях 13, 14 — ыа инверсный.

Таким образом,:-.роизводится изменение выходного напряжения интегратора и, следовательно, частоты генератора 12 в необходимую сторону. Благодаря этой блокировке исключен режим биений частот и устраняется опрокидывание регулирования, о

В установившемся режиме с выхода интегратора 11 снимается постоянное напряжение, при котором управляемый генератор

12 генерирует импупьсы частотой 1 . N > их где f - частота входных импульсов;

К вЂ” емкость счетчика делителя частоты

7, Эти импульсы точно или с некоторой погрешностью синфазны с входными величинами (погрешности синфазности зависят or свойств интегратора, в частности величины дрейфа его нуля)., На один из входов интегратора при этом поступают узкие им,— пульсы, которые компенсируют дрейф нуля интегратора, При изменении по каким-либо причинам частоты входных или обратной свя- 2 зи импульсов, в соответствии со знаком фазового рассогласования импульсов, на один из входов интегратора начнет поступать широтно-импульсный сигнал с выхода триггера

3, Выходное напряжение интегратора 11 при ЗО этом начнет изменяться, что приведет к изменению частоты с выхода управляемого генератора,,12 до величины, когда будет устранен фазовый сдвиг между импульсами входной и обратной связи и появится нулевой сигнал на входе интегратора. Ввиду того, что в установившемся режиме входной сигнал интегратора близок к нулю, то постоянную времени интегратора 11 можно выбрать достаточно малой, и тем самым обеспечить вМ40 сокое быстродействие умножитепя.

При резком изменении входной частоты в течение одного или двух периодов этой частоты, скважность широтно-импульсного

45 сигнала, снимаемого с выходов триггера

3, увеличивается от 0 до I, скачком изменяя величину напряжения на выходе интегратора 11 и входную частоту генератора

12.

С.равнительные испытания предлагаемого устройства с известным устройством показали, no введение новых элементов дало возможность обеспечить мгновенную точность умножения частоты не хуже 0,05%.

Исключение, из схемы устройства таких элементов как yf -разрядные суммирую« шие и вычитающие счетчики позволило конструктивно упростить и увеличить надежность устройства для умножения частот, формула изобретения

Устройство для умножения частот, содержашее триггеры, элементы И,генератор управляемой частоты, подключенный выходом к выходу устройства и входу делители частоты, соединенного выходом с первым входом первого элемента И, второй вход которого подключен к первому входу второго элемента И и первому выходу п рвого триггера, соединенного вторым выходом с первыми входами третьего и четвертого элементов И, причем второй вход третьего элемента И соединен с первым выходом второго триггера, подключенного первым входом к выходу первого элемента И, а первый вход третьего триггера соединен с входом устройства,отличаюшееся тем, что, с целью упрошения устройства и повышения точности умножения, в него введены элемеНты,задержки и интегратор, соединенный входами с выходами второго и третьего элементов И, а выход интегратора соединен с входом генератора управляемой частоты, причем второй вход второго элемента И подключен ко второму выходу второго триггера, соединенного вторым входом с выходом четвертого элемента И, второй вход которого подключен к выходу третьего триггера, соединенного вторым входом с выходом устройства,и к входу первого элемента задержки, выход которого соединен с первым входом первого триггера, подключенного вторым входом через второй элемент задержки к выходу делителя частоты.

Источники информации, принятые во внимание при экспертизе:

1, Шахов Э, К. Тарасов В. ф, Широко т полюсный умножитель частоты с обратной связью и коррекцией по периоду. Измерп тельная техника, 1967, N4,,с.39.

2. Авторское свидетельство CCCf

¹ 416840, кл. Гл 06 7/39 1974

3. Авторское свидетельство ССГР

¹ 404085, кл. (3 06 Р 7/39, 1971.

Составитель С. 1(азинов

Редактор 11 Xaygoaa Техред Л, Богдан Корректор М д

Заказ 1 88/36 Тираж 818 Подписное

Ц11ИИПИ I oñóäàðñòâåííîãî комитета Совета Министров СС..1 по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент, г. Ужгород, ул. Проектная, 4