Импульсный логарифмический усилитель

Иллюстрации

Показать всеРеферат

Союз Советских

Соцналнстнческнх

Республнк

111 5 7 7 Гъ

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву—

2 (51) М. Кл.

С; 06 С> 7/24 (22) Заявлено14.11.75 (21)2190614 18-24 с присоединением заявки № (23) Приоритет— (43) Опубликовано 25.10,77 Бюллетень №8 (45) Лата опубликования описания 14.11.77

Гасударственный намнтет

Сапата Мнннстрав СССР па делам нзааретеннй н аткрытнй (53) УДК 681.335 (088.8) Л. М. Жаворонков, В. Н. Лапенко и H. Н. Шишкевич (72) Авторы изобретения (71) Заявитель

Московский институт электронной техники (54) ИМПУЛЬСНЪ|Й ЛОГАРИФМИЧЕСКИЙ УСИЛИТЕЛЬ

Изобретение относится к вычислительной технике и может найти применение в устройствах первичной обработки информации.

Известен логарифмический видеоусилитель, состоящий из последовательно соединенных усилительных каскадов, фазируюших цепей и суммирующей цепочки 111 . Этому усилителю свойственны низкая стабильность 10 и точность получения логарифмической характеристики при усилении импульсов наносекундного диапазона.

Наиболее близкое к изобретению устрой- 15 ство состоит из последовательно соединенных усилительных каскадбв с регулируемым коэффициентом передаЧи, выходы которых через последовательно соединенные блок пиковых детекторов и аналоговый коммутатор подключены к входам сумматора, и распределительных импульсов 2 .

11ель изобретения — повышение стабильности и точности устройства. 25

Для этого в импульсный логарифмический усилитель введены аналоговый запоминающий блок, блок выработки и хранения корректируюших сигналов, логический элемент ИЛИ и генератор контрольной серии импульсов, выходом соединенный с первым входом логического элемента ИЛИ, второй вход которбго подключен к источнику входного сигнала, а выход — к входу первого усилительного,каскада с регулируемым козффициентОм передачи. Выход последнего усилительного каскада с регулируемым коэффициентом передачи соединен с входом распределителя импульсоВ, выходы которого подключены к управляющим входам блока пиковых детекторов, аналогового коммутатора, генератора контрольной серии импульсов, аналогового запоминающего блока и блока выработки и хранения корректирующих сигналов. Сигнальные входы аналогового запоминаюшего блока и блока выработки и хранения коррек тируюшях сигналовподклточены K выходу сум- ° матора, причем выходы блока выработки и хранения корректирующих сигналов соедине-, ны с управляющими входами усилительных

577542

3 каскадов. с регулируемыми коэффициентами передачи, а выход аналогового запоминаюшего блока подключен к выходной клемме . устройства.

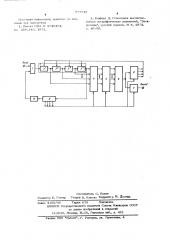

На чертеже изображена структурная схема импульсного логарифмического усилителя.

Импульсный логарифмический усилитель содержит логический элемент ИЛИ 1, выход которого связан с входом импульсного усилителя 2, состояшего из-последовательно соединенных усилительных каскадов 3

3 с регулируемыми коэффициентами передачи> выходы которых соединены с сигнальными входами блока пиковых детекторов 4, Выходы последних соединены с сигнальными входами аналогового коммутатора 5, выходы которого подключены к входам сумматора 6, а его выход соединен с сигнальными входами аналогового запоми.нающего блока 7; и блока 8 выработки и 20 хранения корректирующих сигналов. Выход блока 7 подключен к выходной клемме уст ройства, а выходы блока 8 соединены с управляющими входами усилительных каскадов

3..., 3 с регулируемыми коэффициента-, 5 к и ми передачи Вход распределителя импуль- сов 9 соединен с выходом импульсного усилителя 2, а выходы — с управляюшими входами блоков 4, 5, 7, 8 и генератора конт:рольной серии импульсов ХО. Выход послед- у него соединен с первым, входом, логического элемента ИЛИ 1, а вырой вход элемента ИЛИ 1 подключен к источнику входнот о сигнала, .

Имп фьсный логарифмический усилитель работает следующим образом. Входной импульс через логический элемент ИЛИ 1 поступает на:вход импульсного усйлителя 2.

Выходные импульсы каскадов 3..., 3 40

И ,одновременно поступают на входы блока пиковых детекторов 4, на выходах которого

:йоявляются квазипостоянные напряженйя, KoTopple через аналоговый коммутатор 5 сум:мируются в блоке 6. На выходе последйего 45 реализуется логарифмическая характеристика и выходное напряжение запоминается в аналоговом запоминаюшем блоке 7.

Выходной импульс с импульсного усили- 50 теля 2 поступает на вход распределителя импульсов 9, а с выхода последнего по окончанию процессов восстановления чувствите)тьности усилителя управляюший импульс запускает генератор 10, сбрасывает блок 55 пиковых детекторов 4, настраивает аналоговый коммутатор 5 на последовательное подключение входа, соответствующего каждому усилительному каскаду через блок 6 к блоку 8 и блокирует вход блока 7, 60

Генератор контрольной серии импульсов

10 формирует серию контрольных импульсов, число которых равно ц, т.е. числу каскадов усилителя 2, а отношение амплитуды каждого из предыдуших к амплитуде последующего равно требуемому коэффициенту усиления усилительного каскада, причем амплитуда первого из серии импульсов равна отношению эталонного напряжения к требуемому коэффициенту усиления каскада 3 . Перй вый импульс предназначен для контроля первого каскада 3, второи — для второго 3

1 и т.д. Выходные импульсы каскадов 3

3 через блоки 4, 5, 6 поочередно поступают на вход блока 8, где амплитуды их сравниваются с эталонным напряжением.

Корректирующие сигналы хранятся в блоке

8 и подстраивают коэффициенты усиления каждого каскада 3, 3 до номинального значения.

Формула изобретения

Импульсный логарифмический усилитель, содержащий последовательно соединенные усилительные каскады с регулируемыми коэффициентами передачи, выходы которых через последовательно соединенные блок пиковых детекторов и аналоговый коммутатор подключены ко входам сумматора, и распределитель импульсов, о т л.и ч а ю ш и и с я тем, что, с целью повышения стабильности и точности устройства, в него введены аналоговый запоминающий блок, блок выработки и хранения корректируюших сигналов, логический элемент ИЛИ и генератор контрольной серии импульсов, выходом соединенный с первым входом логического элемента ИЛИ, второй вход которого. подключен к источнику входного сигнала, а выход — к входу первого усилительного каскада с регулируемым коэффициентом передачи, выход последнего усилительного каскада с регулируемым коэффициентом передачи соединен с входом распределителя импульсов, выходы которого подключены к;управляюшим входам блока пиковых детекторов, аналогового коммутатора, генератора контрольной серии импульсов, аналогового запоминаюшего блока и блока выработки и хранения корректируюших сигналов, сигнальные входы аналогового запоминаюшего блока и блока выработки и хранения корректируюших сигналов подключены к выходу сумматора, причем выходы блока выработки и хранения корректирующих сигналов соединены с управляюшими входами усилительных каскадов с. регулируемыми коэффициентами передачи, а выход аналогового запоминаюшего блока подключен к выходной клемме устройства.

177542

Составитель C. Белан

Редактор Е. Гончар Техред И. Климко Корректс.р М. Йемчйк.

Заказ 4186/36 Тираж 818 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушскги наб., д. 4/5

Филиал ППП Патент", г. Ужгород, ул. Проектнаи, 4

Источники информанни, нринятьн во вниманн» нри чкспс ртизе, 1. Пят нт (;IIIA М 3745474, кл. 3 28 — 1 45, 197 3.

2, Клифорл Д. Реализация высокочастотных логарифмических усилителей, "Электроника, русский перевод, No. 3, 1972, с. 46-50.