Триггерное устройство

Иллюстрации

Показать всеРеферат

О и тгЙ- А-и и е

ИЗОБРЕТЕНИЯ

Союз Советских

Социалистических

Республнк (11) 577646

К АВТОУСКОМ3 СВИДИТВЛЬСТВМ (6l) Дополнительное к авт. свнд-ву (22) Заявлено 11.11.74 (21) 2074078/18 1 с присоединением заявки № (23) Приоритет— (43) Опубликовано 25.10.77. Бюллетень ¹3 (45) Дата опубликования описания 10.11.77

Н 03 К 3/286

Гвеудеретвеюпий кееепет

Ввйете Ваеетрвв ССР ее Мехам ееебретееей е еткрытей (53) УДК 621.375.3 (088.8) (72) Авторы изобретения

В. Я. Браславский н А. И. Сегал (71) Заявитель (54) ТРИГГЕРНОЕ УСТРОЙСТВО!

20

Изобретение относится к импульсной технике.

Известен триггер с защитой от помех, содержащий зальчощнй триггер с двумя устойчивымн состояниями, соединительную схему, второй управляемый триггер, источник тактовых сигналов. возбуждающий транзистор !! .

Данное триггерное устройство не обладает достаточной помехоустойчивостью.

Наиболее близким по технической сущности к изобретению является триггерное устройст- . во, содержащее RS-триггер, S входы которопо соединены с выходами двух многовходовых логических элементов И-НЕ. а R вхолы

RS-триггера — с выходами двух других многопходовых логических элементов И-НЕ. Причем трн входа каждого многовхоЛового логического элемента И-НЕ соединены со входами устройства, а два других подключены к выходам соответствующих многовходовых логических элементов И-НЕ противоположной из упомянутых групп многовходовых логических элементов

И-.НЕ 12).

Целью изобретения является повышение помехозащищенности.

Это лостигается тем, что в триггерпое устройство, содержащее RS-триггер, S входы которого соелинены с выходами двух многовхоловых логических элементов И-НЕ, а R входы

RS-триггера с выходами двух других многовхоловых логических элементов И-НЕ, причем три вхола каждого многовходового логического элемента И-НЕ соединены со входами устройства, а лва других подключены к выходам соответствующих многовходовых логических элементов И-НЕ противоположной из упомянутых групп многовходовых логических элементов

И-НЕ, введены лва элемента памяти, каждый из которых выполнен из двух двухвходовых логических элементов И-НЕ с перекрестными связямн между ними. Причем входы элементов памяти соелннены с выходами RS-триггера, а выходы элементов памяти подключены к дополнительным входам многовходовых логических э.цементов И-НЕ.

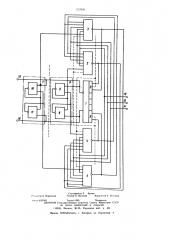

На чертеже приведена структурная электрическая схема описываемого устройства.

Триггерное устройство состоит из К3трнггера 1, S-входы которого соединены с выходамн многовходовых логических элементов

И-НЕ 2 и 3, a R-входы — с выходамн многовхоловыv логических элементов И-HF. 4 и 5, элементов памяти 6, 7, выполненных на лBvxBvojloвых логических элементах И-НЕ 8 — 11. Выхолпые сигналы поданы на входы 12- — 14, а выходные сигналы снимаются с выходов 15 н 16.

577646

Принцип работы устройства заключаетси в следующем.

При поступлении сигнала на один из вколов, например !3, управляющего сигнала, который представляет собой низкий логический уровень, на выходах многовхоловых логических элементов И-НЕ 2 — 5 устанавливается высокии логический уровень, и триггер 1 устанавливается в состояние, при котором на его выходной шине (выходе 16) устанавливается высокий логический. уровень, а на другой шине (выходе jI ! 5) — низкий.

Низким логическим уровнем с выхода

15 элемемты памяти 6 и 7 устанавливаются в состояние, при котором на выходах двухвходо вых логическйх элементов И-НЕ 8, 10 будет высокий логический уровень, а на выхолах двухвхоловых логических элементов И-НЕ 9, i!— низки й.

После снятия управляющего сигнала со входа 13, на выходах многовходовых логических элементов И-НЕ 2, 3 устанавливается низкий 20 логический уровень, а на выходах многовходовых логических элементов И-НЕ 4, 5 остается высокий логический уровень. Низкий логический уровень с многовходовых логических элементов И-НЕ 2, 3 поступает на вход установки триггера 1, подтверждая его состояние.

В случае опрокидывания от действия помех дополнительных элементов памяти триггер 1 не изменяет своего состояния, так как хотя бы на одном из его входов установки 1 Ri будет присутствовать низкий логический уровень, улерживающий его в нредыдуц(ем состоянии.

Дальнейшее увепичение помехоустойчивости может быть достигнуто дополнительным увели цнием количества элементов памяти и многовхоловых логических элементов И-HF.

Форм ила изобретения

Триггерное устройство солержаш<

RS-триггер, S входы которого соединены с вы холами лвух многовходовых логических элсмен тов И-НЕ, à R вхолы RS-триггера -- с выходами двух других многовходовых логических элементов И-HF., три входа каждого многовхолового логического элемента И-НЕ соединены с» вхолами устройства, а лва лругих подклк>чены к выхолам соответствующих многовходовых логических элементов И-НЕ противоположной из упомянутых групп многовходовых логических элементов И-НЕ, отличающееся тем, что, с целью повышения помехозащищенности, в него ввелены лва элемента памяти, каждый из которых выполнен из двух Лвухвхоловых логических элементов И-HE с перекрестными связями между ними, причем вхолы элементов памяти соелинены с выходами RS-триггера, а выхолы элементов памяти подключены к дополнительным вхолам многовхоловых логических элементов

И-HF..

Источники информации, принятые во внимание при экспертизе:

1. Заявка Франции № 2216719 кл

ii 03 К 3/286, 04.!0.74.

2. Авторское свнлетельство СССР № 387528, кл. Н 03 К 29/00, 27 09.73.

577646

Составитель Т. Артвя

Техред О. Луговая Корректор C И екмар

1 гзактор Л. Народная

Филиал ППП аПатентъ, г. Ужгород, ул. Проектная, 4

1аказ 4197/42 Тираж 1065 Подписное

Щ1ИИПИ Государственного комитета Совета Министров СССР но делам изобретений и открытий

1 13035, Моска а, Ж-35, Рау шска я и аб „д. 4/5