Преобразователь кода в частоту

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советскык

Социалистическик

Респубики (!!) 577б73 (6!) Дополнительное к авт. свид-ву (22) ЗаЯВЛЕНо 0110.75(2!) 2153557/18-21 с присоединением заявки %— (5!} М. Кл.

Н 0З К 1ЭУ20

Гааиааатааааий ааватат

Фааата Ваааатааа N0p аа ааааа ааа5аатааа3 а атаритй (23) Приоритет (б3) УДК681 325 (088. 8) (43) Опубликовано 251077.Бюллетень Эй Эц (45) Дата опубликования описания 221L77

P2) Авторы изобретения

И. Т. Абрамсон, Л. Я . Лапкин и О. A. Ханов (7l) Заявитель (54) HPЕОБРАЭОВАТЕЛЬ КОДА В ЧАСТОТУ

Изобретение может использоваться в устройствах преобразования и кодирования информации вычислительных комплексов.

Известно устройство для преобразования информации иэ двоичного кода в,частотно-импульсную бинарную последовательность, содержащее регистр преобразуемой величины, генератор тактовых импульсов и двоичный умножитель частоты, выходные импульсы которого могут стробироваться выходным вентилем с помощью тактовых импульсов, задержанных на линии задержки 1)

Результатом преобразования информации в таком устройстве является последовательность единиц, частота следования которых пропорциональна преобразуемой величине f= „ N где 1 — частота тактовых импульсов, N- n -разрядный двоичный код, записанный в регистре. Число М будет представлено последовательностью из t4 импульсов двоичного умножителя эа 2 тактов. Ъ Ъ

Недостатком известного устройства является низкое быстродействие. Минимальное время установления частоты, пропорциональной числу N, с и точностью в п разрядов равно ф— секунд.

Целью изобретения является увеличение быстродействия преобразователя двоичного кода в частотную последовательность беэ увеличения тактовой частоты.

Это достигается тем, что в преобразователь кода в частоту, содержащий регистр кода, выходы младших разрядов которого соединены с умножителем частоты, частотный вход которого подключен к генератору тактовых импульсов, введены крмбинационный сумматор, выходные вентили и линия задержки. Выходы старших разрядов регистра соединены со входами комбинационного сумматора, выходы котсрого подключены к выходным вентилям, вторые входы которых соединены с выходом линии задержки, вход которой подключен к выходу генератора тактовых импульсов, а выход умнажителя частоты соединен с другим вх. дом сумматора.

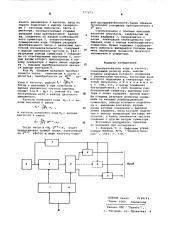

На чертеже изображена структурная электрическая схема преобразователя.

Часть 1 регистра, соответствующая младшим разрядам кода преобразуемой величины, соединена со входами два577673

Формула изобретения каэ 4198/43

5 Подписное

П Патент, ул. Проектная. 4 ичного умножителя 2 частоты, вход ко торого подключен к выходу генератора 3 тактовых. импульсов. Часть 4 регистра, соответствующая старшим разрядам кода преобразуемой величины, соединена со входом комбинационного сумматора 5, осуществляющего суммирование кода старших разрядов преобразуемого числа с единицами частотной последовательности, следующей с выхода умножителя частоты 2. К+1)разрядных выхода сумматора 5 соединены со стробирующими вентилями 6, вторые входы которьс присоединены к выходу генератора 3 через линию эадерж« ки 7. Выходом преобразователя являются выходы вентилей 6.

Код М1 младших разрядов преобразуемого числа, записанный в части 1 регистра, преобразуется эа - — се4и и 29 кунд в частоту, равную 1 2 -ic

Тогда с вентилей 6 при появлении с выхода умножителя частоты единицы сходит код М = Ц2+ 1, равный Ы2 при поступлении нуля с выхода двоичного умножителя.

Частота появления кода M + 1 с выхода вентилей 6 равна .у ти

2и-к Ng 30 а частота появления кода Н2 с выхода вентилей 6 равна ти

Ег -к 2и-к ц

Тогда число М = М2 . 2" " + И будет представлено суммой чисел, поступившей эа 2" " тйктов в виде частотно-кодовой последовательности. Таким образом происходит ускорение преобразования в

2" раз.

Стробирование с помощью выходных вентилей импульсов, задержанных на линии вадержки 7, производится с целью ликвидаций необходимости считывания кода с выхода комбинационного суьиатора. Время задержки стробирующего импульса .,выбирается большим времени переходных процессов двоичного умножителя и сумматора.

Преобразователь кода в частоту, содержащий регистр кода, выходы младших разрядов которого соединены с умножителем частоты, частотный вход которого подключен к генератору тактовых импульсов, о tr. л и ч а ю щ и йс я тем, что, с .целью повышения быстродействия, в него введены комбинационный сумматор, выходные вентили и линия задержки, причем выходы старших разрядов регистра соединены со входами комбинационного сумматора, выходы которого подключены к выходным вентилям, вторые входы которых соединены с выходом линии задержки, вход которой подключен к выходу генератора тактовых импульсов, а выход умножителя частоты соединен с другим входом сумматора.

Источники информации, принятые во внимание при экспертизе:

1. Ходоров Т. Я. Цифровые Управляющие машины. М-, Л„ Машиностроение, 1964. с. 139.