Устройство измерения искажений стартстопных сигналов

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОЛ ИСАНИЕ вттввв

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЙТЙЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 30,03,76 (21) 2341053/09 с присоединением заявки № (23) Приоритет— (43) Опубликовано 25.10.77. Бюллетень №3 (45) Дата опубликования описания 10.11.77 (51) М. Кл.

Н 04 Ь 1/10

Государственный комитет

Совета Министров СССР по делам иэооретений и открытий (53) УДК621,394.662 ° .2 (088.8) (72) Авторы изобретения

Ю. И. Пискуи и 1G И. Попше (71) Заявитель (54) УСТРОЙСТВО ИЗМЕРЕНИЯ ИСКАЖЕНИЙ

СТАРТСТОПНЫХ СИГНАЛОВ

Изобретение относится к телеграфии и технике передачи данных и может использоваться в электроизмерительных приборах узлов связи.

Известно устройство измерения искажений стартстопных сигналов, содержащее входной блок, выход которого подключен к первому входу блока выбора перехода знака сигнала, а ко второму входу блока выбора перехода знака сигнала через формирователь идеального стартстопного знака сигнала, второй выход которого подключен через последовательно соединенные делитель частоты, распределитель и блок элементов И к входам блока элементов памяти (1).

Однако это устройство имеет низкую точность измерения, ограниченную длиной (п разрядов) распределителя.

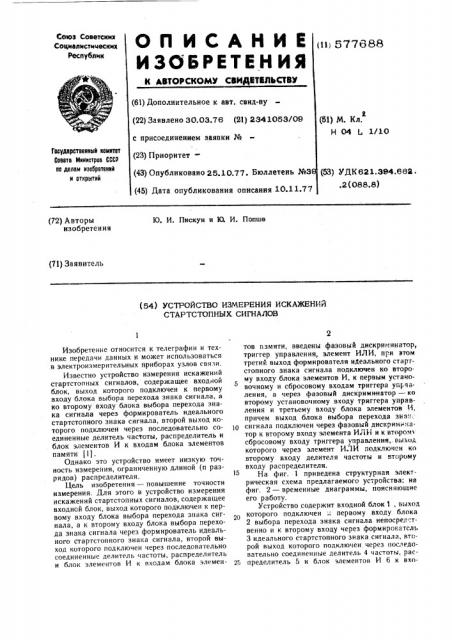

Цель изобретения — повышение точности измерения. Для этого в устройство измерения искажений стартстопных сигналов, содержащее входной блок, выход которого подключен к первому входу блока выбора перехода знака сигнала, а к второму входу блока выбора перехода знака сигнала через формирователь идеального стартстопного знака сигнала, второй выход которого подключен через последовательно соединенные делитель частоты, распределитель и блок элементов И к входам блока элементов пзмяти, введены фазовый дискриминатор, триггер управления, элемент ИЛИ, при этом третик выход формирователя иДеального стартстопного знака сигнала подключен ко второму входу блока элементов И, к первым установочному и сбросовому входам триггера упьавления, а через фазовый дискриминатор — ко второму установочному входу триггера управления и третьему входу блока элементов И, причем выход блока выбора перехода знак. сигнала подключен через фазовый дискрими втор к второму входу элемента ИЛИ и к второю сбросовому входу триггера управления,. выход которого через элемент ИЛИ подключен ко второму входу делителя частоты и второму входу распределителя.

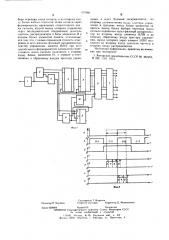

На фиг. 1 приведена структурная электрическая схема предлагаемого устройства; на фиг. 2 — временные диаграммы, поясняющие

его работу.

Устройство содержит входной блок 1, выход которого подключен;; первому входу блока

2 выбора перехода знака сигнала непосредственно и к второму входу через формирователь

3 идеального стартстопного знака сигнала, второй выход которого подключен через носаедовательно соединенные делитель 4 частоты, распределитель 5 и блок элементов И 6 к вхо5?7688 величина отрицательного искажения (по цепи .второпях входа блока элементов И 6 ) При мхом. если зафиксировано отрицательное искажение. то в зоне положительных искажений распределитель 5 продолжает работать до тех пор, пока отрицательным фронтом сигнала (см. фиг. 2б) вторые входы делителя 4 частоты и распределителя 5 не заблокируются в состояние «О» (по цепи триггер 9 управления элемент ИЛИ 10).

При отсутствии отрицательного искажения положительным перепадом триггер 9 управления сбрасывается в состояние «О» и распреде, литель 5 начинает работать (см. фиг. 2ж) также, как и по импульсу со второго выхода фазового дискриминатора 8 (см. фиг. 2д). По импульсу с первого выхода фазового дискриминатора 8 (см. фиг.2е) фиксируется величина положительного искажения с точностью, также равной половине дискретности шкалы, этим же импульсом устанавливается в состояние «1» триггер 9 управления.

Если искажение выбранного значащего момента находится в отрицательной зоне, а искажение соседнего слева значащего момента положительно и превышает величину +50%, то в этом случае первым на втором выходе фаэовопэ дискриминатора 8 появляется ложный нм25 пульс, который запускает ра спредел ител ь 5, однако второй импульс на этом же выходе, соответствующий истинному отрицательному искажению, через первый вход элемента

ИЛИ 10 сбрасывает делитель 4 частоты и распределитель 5 в состояние <0», исключив таким образом действие первого ложного импульса.

Если же искажение выбранного значащего момента находится в положительной зоне, а искажение соседнего справа значащего момента отрицательно и превышает 50%, то в этом случае на первом выходе фазового дискриминатора 8 появляется импульс, соответствующий истинному положительному искажению, которое и зафиксируется в блоке 7 элементов памяти, а ложный импульс, приходящий вторым, только подтверждает блокировку в состояние

4ц «О» делителя 4 частоты и распределителя 5 и фиксирует нулевое положительное искажение, которое не искажает зафиксированное истин ное положительное искажение больше 0%. Таким образом повышается достоверность измерения. В тех случаях, если неверно выбрана шкала измерений, при наличии искажений как в отрицательной зоне, так и в положительной зоне распределитель 5 совершает полный рабочий цикл до момента фиксации искажения, что служит признаком переполнения шкалы.

Данные экспериментальных исследований показали, что в предложенном устройстве на

10 — 20% сокращаются применяемые элементы первым установочному и сбросовому входам триггера 9 управления и через фазовый дискриминатор 8 ко второму установочному входу триггера 9 управления и третьему входу блока элементов И б, причем выход блока 2 выбора перехода знака сигнала подключен через фазовый дискриминатор 8 к второму входу элемента

ИЛИ 10 и ко второму сбросовому входу триггера 9 управления, вчход которого через элемент

ИЛИ 10 подключен ко второму входу делителя

4 частоты и ко второму входу распределителя 5.

На фиг. 2 — а — сигнал на выходе входного блока I, б — сигнал на третьем выходе формирователя 3 идеального стартстопного знака сигнала, в — сигнал иа втором входе блока 2 выбора перехода знака сигнала, r — сигнал на втором выходе фазового дискриминатора 8, д— последовательность сигналов иа выходных шинах распределителя 5, е — сигнал на первом выходе фазового дискриминатора 8, ж — последовательность сигналов на выходных шинах распределителя 5.

Устройство работает следующим образом.

Информационный сигнал (см. фиг. 2а) нз канала с выхода входного блока 1 подается на формирователь 3 и на блок 2 выбора перехода знака сигнала. С первого выхода формирователя 3 снимается сигнал вида (см. фнг. 2в), выбиравший для измерения определенный зна"ащий момент или сигнал, разрешающий измерение всех значащих моментов принимаемого стартстопного знака. С второго выхода формирователя 3 на вход делителя 4 частоты подаются сигналы частоты, задаваемой формирователем 3.

Распределитель 5 начинает свою работу по значащим моментам принимаемого знака, а не по значащим моментам идеального знака формируемого формирователем 3. flo отрицательно— му перепаду сигнала с третьего выхода формирователя 3 {см. фиг. 26} триггер 9 управлениг устанавливается в состояние «l » и через эл =мент ИЛИ 10 единичный сигнал с выхода триггера 9 управления удерживает делитель

4 частоты и распределитель 5 в состоянии «О»

При этом в случае отсутствия значащего момента в зоне отрицательных искажений, определяемой нулевым уровнем сигнала (см. фиг.

2б) по положительному перепаду указанного сигнала в блоке элементов И 6 срабатывает соответствующий элемент И, а в блоке 7 элементов памяти фиксируется нулевое искажение.

11ри наличии же в указаннон зоне знача:цего момента искаженной посылки импульсом (см. " нг. 2г) с второго выхода фазового дискрн;.ннатора 8 триггер 9 управления сбрасывается в состояние «О» и нулевое состояние дели55 теля 4 частоты и распределителя 5 раэблокнровывается.

По положительному перепаду сигнала (см. фиг. 2б) соответствующему положению идеального значащего момента, фиксируется 6

Формула изобретения дам блока 7 элементов памяти, фазовый дискриминатор 8, триггер 9 управления, элемеи1

ИЛИ 10, при этом третий выход формирователя

3 идеальиого.стартстопного знака сигнала подключен к второму входу блока элементов И 6, к за счет исключения коммутатора и уменьшения в два раза длины распределителя, а также повышается точность результатов измерения.

Устройство измерения искажений сг.ip- топных сигналов, содержащее входной блок, -. ход которого подключен к первому входу блок„ ны, 77688

Фиг f фма.2

Составитель T. Маркина

Техред О. Луговая Корректор Д. Мельниченко

Редактор Н. Хлудова

Заказ 4200/44 Тираж 815 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

118()35, Москва, Ж -35, Раушская наб., д. 4!5

Филиал П1111 <Патент>, г. Ужгород, ул. Проектная, 4 бора перехода знака сигнала, а ко второму входу блока выбора перехода знака сигнала через формирователь идеального стартстопного знака сигнала, второй выход которого подключен через последовательно соединенные делитель частоты, распределитель и блок элементов И к входам блока элементов памяти, отличающееся гем, что, с целью повышения точности измерения, в него введены фазовый дискриминатор, триггер управления, элемент ИЛИ, при этом третий выход формирователя идеального стаотстопного знака сигнала подключен к второму входу блока элементов И, к первым установочному и сбросовому входам триггера управления, а через фазовый дискриминатор --- ко второму уста ново ч ному входу > ри г гера у и ра вления и третьему входу блока элементов И, причем выход блока выбора перехода знака

5 сигнала подключен через фазовый дискриминатор ко второму входу элемента ИЛИ и ко второму сбросовому входу триггера управления, выход которого через элемент ИЛИ подключен ко второму входу делителя частоты и второму входу распределителя.

Источники информации, принятые во внимание прн экспертизе:

1. Авт вторское свидетельство СССР pro 48 9

Н 041 1/1О, 1974.