Устройство для определения скорости телеграфирования

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОП ИСАНИЕ (11) 5776г:1 »

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 04.01.76 (21}2312409/18-0 с присоединением заявки № (23) Приоритет (43) Опубликовано 25.10.77, Бюллетень №3 (51) М. Кл.

Н 04 L 7/04

Государственный комитет

Совета Мкннстроа СССР оо делам изобретений н открытий (53) УДК 621.394.662 (088.8) (45) Дата опубликования описания 10.11,77 (72) Авторы изобретения

H. Л. Храпова, В. Г. Слюсарь и В. С. Фридман

Иркутский завод радиоприемников им. 50-петия СССР (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ СКОРОСТИ

ТЕЛЕГРАФИРОВАНИЯ

Изобретение относится к электротехнике, в частности к устройствам для анализа и измерения параметров принимаемых телеграфных посылок н может использоваться в системах, принимающих как старт-стопные, так и синхронные передачи.

Известно устройство для определения скорости телеграфирования, содержащее последовательно соединенные преобразователь входных сигналов н блок квантования к второму входу которого подключен первый выход гене- 1О ратора опорных частот, а также формирователь сигнала «сброс», блок пересчета и блок индикации (lj.

Целью изобретения является повышение точности определения скорости телеграфироваI;> ни я.

Для этого в устройство для определения скорости телеграфирования, содержащее последовательно соединенные преобразователь входных сигналов и блок квантования, к второму входу которого подключен первый выход генератора опорных частот, а также формирователь сигнала «сброс», блок пересчета и блок индикации, введен блок выделения элементарного периода входных сигналов, при этом выход

f).þêà квантования через последовательно соединенные блок выделения элементарного периода входных сигналов, управляющий выход которого подключен к третьему входу блока квантования, и блок пересчета, второй и третий входы которого соединены соответственно с вторым и третьим выходами генератора опорных частот, подключен к блоку индикации, а второй выход преобразователя входных сигналов через формирователь сигнала «сброс» подключен к управляющему входу блока выделения элементарного периода входных сигналов. Последний состоит из последовательно соединенных суммирующего счетчика, реверсивного счетчика н дешифратора нулевого состояния реверсивного счетчика, а также элемента памяти, при этом выход блока квантования подключен к объединенным входам синхронизации суммирующего и реверсивного счетчиков, выходы формирователя сигналов «сброс» подключены к установочным входам суммирующего счетчика и реверсивного счетчика я элемента памяти, выход которого подключен к первому входу блока пересчета, причем к входу элемента памяти подключен другой выход суммирующего счетчика, а выход дешнфратора нулевого состояния реверсивного счетчика подключен к третьему входу блока квантования.

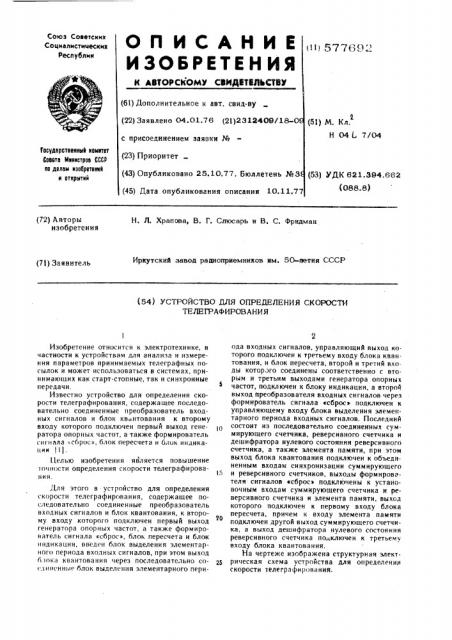

На чертеже изображена структурная элект. рическая схема устройства для определения скорости теле гра фи рован и я.

577692

15

Формула изобретения

4Î

35

60

Схема содержит последовательно соединенные преобразователь входных сигналов и блок квантования 2, к второму входу которого подключен первый выход генератора 3 опорных частот, а также формирователь 4 сигнала

«сброс», блок пересчета 5 и блок индикации 6, введенный блок выделения 7 элементарного периода входных сигналов, при этом выход блока квантования 2 через последовательно соединенные блок выделения 7 элементарного периода входных сигналов, управляющий выход которого подключен к третьему входу блока квантования 2, и блок пересчета 5, второй и третий входы которого соединены соответственно с вторым и тр тьим выходами генератора 3 опорных частот, подключен к блоку индикации 6, а второ" выход преобразователя 1 входных сигналов через формирователь 4 сигнала «сброс» подключен к управляющему входу блока выделения 7 элементарного периода входных сигналов.

Блок выделения 7 элементарного периода входных сигналов состоит из последовательно соединенных суммирующего счетчика 8, реверсивного счетчика 9 и дешифратора 10 нулевого состояния реверсивного счетчика, а также элемента памяти 11, при этом выход блока квантования 2 подключен к объединенным входам синхронизации суммирующего и реверсивного счетчиков 8 и 9. Выходы формирователя 4 сигнала «сброс» подключены к установочным входам суммирующего счетчика 8 и реверсивного счетчика 9 и элемента памяти 1, выход которого подключен к первому входу блока пересчета

5, причем к входу элемента памяти 11 подключен другой выход суммирующего счетчика 8.

Выход дешифратора 10 нулевого состояния реверсивного счетчика подключен к третьему входу блока квантования 2.

Устройство для определения скорости телеграфирования работает следующим образом.

Сигнал, поступающий на преобразователь i, очищается от шумов, формируется в прямоугольные импульсы и подается на один из входов блока квантования 2, на другой вход которого подается кварцованная частота с выхода генератора 3. Пачки импульсов с блока квантования 2 поступают параллельно на входы синхронизации суммирующего 8 и реверсивного

9 счетчиков. Первый период посылки, заполненный кварцованной частотой, записывается в суммирующий и реверсивный счетчики. Затем импульсам, поданным с формирователя 4, триггеры реверсивного счетчика 9 устанавливаются в нулевое состояние, после чего код, записанный в суммирующий счетчик 8, параллельно переносится в реверсивный счетчик 9. Триггеры суммирующего счетчика 8 устанавливаются в первоначальное нулевое состояние. Вспомогательнь1е импульсы формируются путем задержки заднего фронта периода принимаемого сигнала формирователя 4. Второй период посылки, заполненный кварцованной частотой, записывается в суммирующий счетчик 8, а в реверсивном счетчике 9 происходит вычитание первого периода из длительности второго периода. Как только периоды сравнивакггся по длиге1ьно и, Д на выходе дешифратора 10 появляется низкий потенциал, запирающий блок квантования 2 и отключающий сигнал на входе блока выделения 7. Если один из приходящих периодов элементарный, то он автоматически контролирует по длительности все следующие периоды. Выделенный элементарный период в виде кода с суммирующего счетчика 8 переносится в элемент памяти 11, с которого он поступает в блок пересчета 5. Блок пересчета 5 пересчитывает код элементарного периода в число, соответствующее скорости телеграфирования, которое и высвечивается индикатором блока индикации 6.

Процесс анализа входного сигнала повторяется с приходом каждой новой посылки.

Предлагаемое устройство для определения скорости телеграфирования обладает повышенной помехозащищенностью и более точным определением скорости телеграфирования.

l. Устройство для определения скорости телеграфирования, содержащее последовательно соединенные преобразователь входных сигналов и блок квантования, к второму входу которого подключен первый выход генератора опорных частот, а также формирователь сигнала

«сброс», блок пересчета и блок индикации, отличающОЕся тем, что, с целью повышения точности, введен блок выделения элементарного периода входных сигналов, при этом выход блока квантования через последовательно соединенные блок выделения элементарного периода входных сигналов, управляющий выход которого подключен к третьему входу блока квантования, и блок пересчета, второй и третий входы которого соединены соответственно с вторым и третьим выходами генератора опорных частот, подключен к блоку индикации, а второй выход преобразователя входных сигналов через формирователь сигнала «сброс» подключен к управляющему входу блока выделения элементарного периода входных сигналов.

2. Устройство по п. 1, отличающееся тем, что блок выделения элементарного периода входных сигналов состоит нз последовательно соединенных суммирующего счетчика, реверсивного счетчика и дешифратора нулевого состояния реверсивного счетчика, а также элемента памяти, при этом выход блока квантования подключен к объединенным входам синхронизации суммирующего и реверсивно .о счетчиков, выходы формирователя сигнала «сброс» подключены к установочным в одам суммирующего счетчика и реверсивного счетчика и элемента памяти, выход которого подключен к первому входу блока пересчета, причем к входу. элемента памяти подключен другой выход суммирующего счетчика, а выход дешифратора нулевого состояния реверсивного счетчика подключен к третьему входу блока квантования.

Источники информации, принятые з внимание при экспертизе:

1. Авторское свидетельство СССР . Ъ 383218, М. кл. . 1-1 04 L 7/02,.1973.

577692

Составитель A. Грачев

ТехредО. Луговая Корректор Д. Мельниченко

Рс:диктор Е. Гончар

Филиал IIIIII «Патент, г Ужгород, ул Проектная, 4

Заказ 420044 Тираж 8!5 Подписное!!!!ИИГ!И Государственного комитета Совета Министров С(.(.Р по делам изобретений и открнтн4! I:3035, Москва, Ж-35. Раугнская наб., д. 4/5