Устройство для передачи информации разностными сигналами

Иллюстрации

Показать всеРеферат

ОПИСАИИТ

Союз Советскик

Социалистимескиз

Республик (11) Ь77(ц7

ИЗОБРЕТЕИМЯ

К АВ 1 ОРСКОМУ СВИДЕТЕЛЬСТВУ (б1) Дополнительное к авт. свид-ву (22) Заявлено 01Яб76 (21) 236 8б24/18-09 с присоединением заявктт № (23) Приоритет— (43) Опублттковано 25,1077.6толлетеиь В 39 (45) Дата опубликования описвтн" и н 04 (25/02

Н 03 К 13/22

Й41Щетееееы1 Веаетьт

Февете МВВВВТРВВ ВСВОЕ

44 Вевеа Взвбретеий

В етерытей (ь4 @- 621,376,5 (088.8> (72) Авторы изобретения

Р. Т. Сафаровг B.В,Коваль к А.Ю.КОльцов (71) Заявитель, 54) УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ИНфОР11АШ131

РАЗНОСТНЬМИ СИРНАЛАИИ

Изобретение относится к технике связи, в частности к устройствам для передачи информации разностными сигналами.

Известно устройство для передачи информации разностными сигналами, содержащее на входе преобразователь аналог-код, выходы КОторого подключены к одним входам блока вычитания, а к

его другим :входам подключены выходы 10 сумматора. Выходы блока вычитания подключены к !соответствующим входам формирователя выходных импульсов, тактовый вход которого соединен с выходом синхронизатора и с соответствую- 15 щими входами преобразователя аналогкод, блока вычитания и сумматора. К управляющему входу сумматора подключен один из выходов,триггера, а к информационным входам — соответствующие Ю выходы матричного коммутатора, к управляющему входу которого подключен выход блока задержки. (1

Однако известное устройство для пе- 95 редачи информации разнастнымк сигналами обладает большой дисперсией ошибки перегрузки и большим количеством посылок, необходимых для передачи приращений сигнала. И

Целью изобретения являет-я уменьшение дисперсии Ошибки перегрузки и уменьшение количества посылок, необходимых для передачк приращений сигналаа.

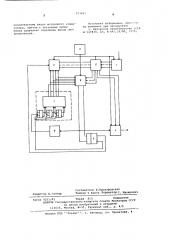

Дпя этОГО B известнОе g OTpoAOTBo для передачи информации разнастныии сиГналамк B oÄÁII блОк сравнениB вклЮ ченный между выходам матричнorо коммутатораи допалнительньъи выходамк блока вычитания, при этом единичный выход блока сравнения подключен к соответствующе входу триггера, к дополнительному входу формирователя выходных импульсов и к входу блока задержки, а нулевой выход блока.сравнения подключен к другому тсответствующему входу триггера, другой выход котарагo.ïoäêëIo÷åí к даполнктельному входу матричного коммутатора, причем к тактовому входу блока сравнения пОдключен вйхОд синхрОнизатОра, на чертеже приведена1функцканальная электркческая хема.

Устройства для передачи информации разностными скгналами содержит на вхаде преобразователь аналог-код 1, выходы катарОГo подключены к Одним вхо дам злака вычитания 2, B к его другим входам ИОдключены выходы с чо1атара 3

577697

Выходы блока вычитания 2 подключены к соответствующим входам формирователя

4 выходных импульсов, тактовый вход которого соединен с выходом!синхронизатора 5 и с соответствующими входами преобразователя аналог-код 1, блока вычитания 2 и сумматора 3. К управляющему входу последнего. подключен один иэ выходов триггера 6, а к информационным входам — соответствующие выходы матричного коммутатора 7, к управляющему входу которого подключен выход блока задержки 8. Блок срав. нения 9, включен между! выходом матричного коммутатора 7 и дополнительны ми выходами блока вычитания 2, при этом единичный выход блока сравнения 9 подключен к соответствующему входу триггера 6, к дополнительному входу формирователя выходных импульсов 4 и к входу блока задержки 8, а нулевой выход блока сравнения 9 подключен к другому соответствующему входу триггера 6, Другой выход .этого триггера подключен к дополнительному входу матричного коммутатора 7, причем к тактовому входу, блока сравнения 9 подключен выход синхронизатора 5.

Устройство работает следующим обра" эом. Синхронизатор 5 .управляет работой основных блоков. Сообщение Л(1) с помощью преобразователя аналог-код 1 преобразуется в параллельный двоичный код, цифровой сигнал Л кэ (t4 ) с выхода преобразователя аналог-код 1 пос- Ж тупа".т на вход блока вычитания 2, на вторую группу входов которого подается сигнал Au(t(-1 ) с выхода сумматора 3. В момент времени ti в блоке вычитания 2 производится вычитание 40

Лц(М-t ) из ilкв (1Л ), В результате вычитания на первых двух выходах блока вычитания 2 .вырабатывается сигнал + (ь (ti ))О), или - (Ь (tj )

Сигналы + и - .подаются на второй и третий входы формирователя 4 выходных импульсоэ; с второй группы выходов результат вычитания параллельным двоичным кодом подается на пер- бр вую группу входов блока сравнения 9, на вторую группу входоэ которого с выхода матричного коммутатора 7 подается параллельным двоичным кодом сигнал, отображающий вес последующего Разряда. ó

Матричный коммутатор 7 ипата выходов, соединенных с входами бЛОка сравнения 9. Вес сигналов на я входах

Выходы матричного коммутатора 7 с

2 до Il -го также соединены с входами (я-1 ) сумматора 3, Однако вес сигналов на входах сумматора равен 2 2 n-Z

4 Ф ° ° f Г

В результате сравнения сигнала раэ. ности а, поступающего э блок сравнения 9 с выхода блока вычитания 2, с весовым сигналом, поступающим в блок сравнения 9 с выхода матричного коммутатора 7, на выходе блока сравнения 9 формируются сигналы 1, если результат сравнения 30 или О если сравнения с О.

При формировании сигнала 1 в канал связи выдается посылка. Одновременно сигнал 1 через блок задержки 8 подается на вход матричного коммутатора 7, на выходе .которого возникают сигналы, подлежащие суммированию. Эти сигналы поступают на входы сумматера 3, увеличивая записанное в нем число на 1, 2, 4 и т.д. при подаче всего одного входного сигнала.

При формировании на выходе блока сравнения 9 э сигнале О триггер б переходит в проТивоположное состояние и переводит триггеры матричного коммутатора 7 в исходное состояние.

Сигналы с прямого выхода триггера 6 служат для управления операциями суммирования.

Использование предложенйого устройства повышает эффективность систем передачи информации, существенно уменьшает дисперсию ошибки накопления.

Формула изобретения устройстэс для передачи информации разностными сигналами, содержащее на входе преобразователь аналогкод, выходы которого подключены к одним входам блока вычитания, к другим. входам которого подключены выходы сумматора, а выходы блока вычитания подключены к соответствующим " входам формирователя выходных импульсов, тактовый вход которого соединен с выходом синхронизатора и с соответствующими входами преобразователя аналогкод, блока вычитания и сумматора, к управляющему входу которого подключен один иэ выходов трйггера, а к информационным входам - соответствующие выходы матричного коммутатора,йупраэляющему входу которого подключен выход блока задержки, о т л и ч а ю щ е ес я тем, что, с целью уменьшения дисперсии ошибки перегрузки и уменьшения количества посылок, необходимых для передачи приращений сигнала, введен блок сравнения, включенный между выходом матричного коммутатора и дополнительными выходами .блока вычитания, при этом единичный выход блока сравнения подключен к соответствующему входу триггера, к дополнительному входу формирователя выходных импульсов и к входу блока задержки, а нулевой выход блока сравнения подключен к другому соответствующему входу триггера, другой выход которого подключен к до57 7697

Составитель Е.Проэоровская

Техред 3 Фанта Корректор П. Макаревич

Редактор Е.гончар

Эакаэ 4201/45 Тираж 815 Подписное цНИИПИ Государственного "комитета Совета Министров СССР по делам иэобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4!5

Филиал ППП Патент, r. Ужгород, ул. Проектная, 4 полнительному входу митричиого коммутатора, прнч м к тактовому входу блока сравнения подключен выход синхрониэатора.

Источники инФормацин, прив во внимание при экспертизе:

1, Авторское свидетельство С:CP

М 527834, кл. Н 04 Ь 25/00, 19 ?5.