Цифровой линейный интерполятор

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

Союз Советскии

Социапистическик

Респубпик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (6)} Дополнительное к авт. саид-ву(22) Заявлено 222776 (21)2393877/18-24 с присоединением заявки Ph(23) Приоритет(43) Опубликовано 051).77. Бюллетень ЭВ 41 (45) Дата опубликования описания 24.11.77 (Sэ М. Кл.

G 05 В 19/18

ТЭЭРДЭРЭТЭЭЭЭЯЭ ЭЭЯЭТЭТ

Сэээтэ Мээээтрээ ИВР

° Э IIII1 IIIIPITIIII

I ITIPiITIN (53) УДК 621. 503.55 (088.8>

A.È.Âîëêîâ и Г.Е.Ставицкий (72) Авторы изобретения (71) Заявитель (54) ЦИФРОВОЙ ЛИНЕЙНЫЙ ИНТЕРПОЛЯТОР

Изобретение относится к области автоматики и вычислительной техники и может быть использовано в выводных графических устройствах с линейными и матричными органами регистрации, а 6 также в станках с программным управлением, в которых использованы линейные и матричные исполнительные органы.

Известен линейный интерполятор, со- )0 держащий собирательную схему, последовательно соединенные регистр, вентили, сумматор и схему анализа знака. один из выходов которой соединен с управляющими входами вентилей. )6

Известен также цифровой линейный интерполятор, содержащий регистры координатных приращений, подключенны . к блоку анализа координатных приращений и через блойи совпадения кодов 20 к элементу ИЛИ.

Недостатком интерполяторов jlj и )2j является низкое быстродействие.

Наиболее близким техническим решением к изобретению является цифро. вой линейный интерполятор, содержащий регистры координатных приращений, подключенные к схеме сравнения, и блок управления, выход которого подключен к управляющим входам двоичного и накапливающего сумматоров (3)

Недостатком этого интерполятора является низкое быстродействие в том случае, если отношение значений координатных приращений не кратно степе ни числа 2.

Цель изобретения — повыщение быстродействия интерполятора.

Поставленная цел достигается тем, что в предложенный интерполятор введены входной коммутатор, входы которого соединены с выходами регистров коордкнатных приращений, делитель координатных приращений, первый и второй входы которого соединены с первым и вторым выходами входного коммутатора, первый выход которого соединен со входом блока управления, блок памяти„ входы которого подключены к выходам делителя координатных приращений, а выходы - ко входам двоичного и накапливающего сумматоров, и выходной коммутатор, первые входы которогс соединены с выходами двоичного cyw:, тора, второй вход — с выходом блока управ— ления, а управляющие входы коммутаторов подключены к выходу схемы сравнения.

579599

l

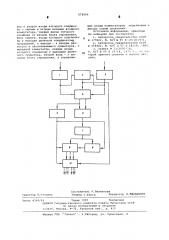

В регистры 1, 2 записываются соответственно приращения Ь Х и Ь У, задающие отрезок. В схеме сраннения 3 осуществляется сравнение величин Ь Х и Л У.Если Ь Х > Ь У, то приращение

Ь У появляется на первом выходе коммутатора 4, входы которого соединены с выходами регистров 1 и 2, а приращение b X — на втором выходе коммутатора 4. Если ДХ (ЬУ, то приращения на выходе коммутатора 4, управляемого сигналом с выхода схемы сравнения

3, меняются местами. Таким образом, на вход блока управления 5 и первый вход делителя 6 всегда поступает мень шее из приращений, а на второй вход делителя б — большее. В делителе 6 осуществляется деление большего. лриращения на меньшее, например Я-. . 1

Пслученное с выхода делителя 6 отноше йие запоминается в блоке 7 и по управляющим тактам иэ блока управления 5 переписывается в сумматоры 8 и 9. При этом целая часть ОтнОшения переписывается в сумматор 8, ЬХ а дробная часть отношения -7(— в

DX сумматор 9. С выхода сумматора 8 целая часть отношения - - поступает

hX на первый вход коммутатора 10, на нто рой вход которого поступают единичные сигналы с выхода блока управления 5.

Коммутатор 10 управляетск сигналом со схемы сравнения 3: при ДХ ьУ первый выход коммутатора 10 соединен с элементами регистрации горизонтального линейного (или матричного) органа регистрации, а второй — co счетчиком строк блока управления органом регистрации (на схеме не показаны), при ЬХ < hY перный выход коммутатора

10 соединен со счетчиком столбцов, а

Схема интерполятора представлена на чертеже.

Он содержнт регистры 1, 2 координатных приращений, подключенные к схеме сравнения 3 и входному коммутато5 ру 4. Первый выход коммутатора 4 подключен к блоку управления 5 и перному входу делителя координатных приращений 6, а второй выход — ко второму входу делителя б, выходы которого подключены к входам блока памяти 7. Выходы последнего соединены со входами двоичного сумматора 8 и накаплинающего сумматора 9, соединенными между собой цепями переноса.

Выходы сумматора 8 подключены к первым входам выходного коммутатора 10, второй вход которого, а также управляющие входы сумматоров подключены ко входам блока управления 5.управляющие входы 10 коммутаторов 4 и 10 подключены к выходу схемы сравнения 3, а выходы коммутатора 10 являются выходами интерполятора.

Интерполятор работает следующим образом. 25 второй — с элементами регистрации вертикального линейного (или матрично го) органа регистрации.

Формирование строки (столбца) в интерполяторе осуществляется за 1 такт. В этом такте отношение

Х из блока 7 поступает на входы сумматоров

8 и 9. В сумматоре 9 осуществляется сложение дробной части отношения - AX с дробной частью предыдущей суммы, а возникающее переполнение из дробных разрядов сумматора 9 переписывается и младший разряд целого сумматора d.

Целая часть полученной суммы из сумматора 8 через коммутатор 10 поступает на выход интерполятора (на регистрирующие элементы), а единичный импульс (такт) из блока управления 5 через коммутатор 10 — в счетчик строк или счетчик столбцов блока управления регистрирующего органа (на схеме не показан).

Число тактов в полном цикле работы интерлолятора не зависит от соотношения приращений и равно величине меньшего из приращений.

AX. npu bX < Ь 1

T цикла йу, при ЬХ > 4у

Сигнал конец интерполирования отрезка вырабатывается и блоке управления 5 после определения равенства между числом выданных управляющих тактов и неличиной меньшего из приращений.

Применение цифрового линейного интерлолятора с делителем увеличивает производительность выводных графических устройств с линейными или матричными органами регистрации по сравнению с цифровым линейным интерполятором с взаимосвязью между временем интерполирования и соотношением координатных приращений, так как в предлагаемом интерлоляторе время интерполирования всегда равно меньшему из приращений, а и прототипе только н предельном случае.

-Формула изобретения

Цифровой линейный интерполятор, содержащий регистры координатных приращений, подключенные к схеме сравнения, и блок управления, выход которого подключен к управляющим входам двоичного и накаплинающего сумматоров, отличающийся тем, что, с целью повышения быстродействия, н него введены входной коммутатор, входы которого соединены с выходами регистров координатных приращений,делитель координатных приращении, лер579599

Составитель Н.Белинкова

Техред З.Фанта Корректор П.Макаревич

Редактор Л.утехина

Заказ 4394/44 Тираж 1095 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, г.ужгород, ул. Проектная, 4 вый и второй входы которого соединены с первым и вторым входами входного коммутатора, первый выход которого соединен со входом блока управления, блок памяти, входы которого подключен ны к выходам делителя координатных приращений, а выходы — к входам двоичного и накапливающего сумматоров, и выходной коммутатор, первые входы которого соединены с выходами двоичного сумматора, второй вход — с выходом блока управления, а управляющие входы коммутаторов подключены к выходу схемы сравнения.

Источники информации, принятые во внимание при экспертизе:

1. Авторское свидетельство СССР

М 377822, М. Кл G 05 В 19/18 1971.

2. Авторское свидетельство СССР

У 259492, М. Кл. С 05 В 19/18, !968.

3. Заявка М 2112695/24, М. Кл 5 05 В 19/1Ь, 19 5 г., па которой принято решение о выдаче авт. сзид.