Устройство для деления

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИЛЕТГЛЬСТВУ

Сккп Саветскнк

Сацналистнчесинк

Рвскяублнк (><) 579614 (6!) Дополнительное к авт. саид-ву— (22) ЗаЯвлено 250375 (2!) 2114929/18-24 с присоединением заявки №вЂ” (23) Приоритет— (43) Опубликовано05,11.77. Бюллетень № 41 (45) Лата опубликования описания 2931.77 (51) М. Кл.

Сэрб Г 7/39 т яарйбрятяяяяия яявятят

Ваватя Мяяяятров ВСЮ яя дяяям яяоярвтяяяя я аткрыткя

{53) Ì

681 325(088 8) (72) Авторы изобретения H. Я. Акушский, В. М. Бурцев, A. О. Жаутыков и И. Т, Пак (7Ц ЗаяянтЕЛЬ Институт математики и механики AH Казахской CCP (54) УСТРОИСТВО ДЛЯ ДЕЛЕНИЯ

Изобретение относится к области вычислительной техники и может быть использовано для выполнения операции деления в системе остаточных классов.

Известны устройства, выполняющие операцию деления чисел, представленных в каком-либо одном позиционном коде и содержащие многоразрядный сумматор, регистр делимого, регистр частичного остатка, входы которых соеди- 10 иены с выходом многоразрядного сумматора, табличный дешифратор, соединенный с выходом регистра частичного остатка, дешифратор коэффициентов умножения, регистр делителя, вход которого подключен к выходу дешифратора коэффициентов умножения, а выход соединен с сумматором111 .

Низкое быстродействие таких устройств обусловлено наличием цепей пере-20 носа в сумматоре.

Наиболее близким техническим решением к изобретению является устройство для деления, содержащее регистр делимого, регистр делителя и сумматор (2) .Его недостатками являются невысокое быстродействие и невозможность работы s системе остаточных классов. целью изобретения является повышение быстродействия за счет выполнения деления чисел в системе остаточных классов.

Эта цель тостигается теМ, что в предложенное устройство введены блок выбора элементарного делителя, блок умножения, блок вычитания, блок анализа произведения, блок конца итерации, блок конца деления, блок режима работы сумматора, блок вычисления итерации.

Выход регистра делимого подключен к первому входу блока вычисления итерации, второй вход которого подключен шине позиционного признака делимого.

Выход регистра делителя подключен ко з .;ipy блока выбора элементарного делителя, к третьему входу блока вычисления итерации и к первому входу блока умножения. Выход блока элементарного делителя подключен к четвертому входу блока вычисления итерации, пятый вход которого подключен к шине позиционного признака делителя и ко второму входу блока умножения, третий вход которого подключен к первому входу сумматора, первому входу блока вычитания, первому входу блока конца деления, к выходу блока вычисления итерации и ко входу блока конца итерации, выход

57.9614 которого подключен ко второму входу блока конца деления и к шестому входу блока вычисления итерации. Выход блока конца деления подключен к четвертому входу блока умножения, к первому входу блока анализа произведения, ко второму входу блока вычитания и ко второму входу сумматора. Выход блока умножения подключен ко второму входу блока анализа произведения, выход которого подключен через блок режима работы сумматора к третьему входу блока вычитания, выход которого подключен к седьмому входу блока вычисления итерации. Выход сумматора соединен с выходом устройства.

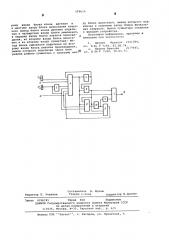

На чертеже дана структурная схема устройства для деления.

Оно содержит регистр делимого 1, регистр делителя 2, блок 3 выбора эле- 2О ментарного делителя, блок я вычисления итерации, блок 5 конца итерации, блок б конца деления, сумматор 7, блок 8 умножения, блок 9 вычитания, блок 10 анализа произведения, блок 11 28 режима работы сумматора, шину 12.позиционного признака делимого, шину 13 позиционного признака делителя, информационные входы 14, 15 и выход 16 устройства для деления. 30

Рассмотрим работу устройства при делении делимого А на делитель В,которые представлены в системе остаточных к ассов своими остатками по основаниям Р,, Р, ..., Р, а именно A = 35

-(,, д...... > v

Блок 3 осуществляет анализ остатка на нуль. если Р =О, то делитель делится на первое основание Р,, à ес- 4р ли Д,Ф О, то делитель В делится на 2 блоком 4 вычисления итерации. Параллельно с этим процессом идет деление делимого А на Р, блоком 4 вычисления итерации, если Д=0,и деление A на 2, если О. Результат деления делителя В айалиэируется блоком 5 конца итерации на его равенство единице, т.е. В = 1.

Если В =1, то выполняются вышеописанные

i действия, но уже с В . Если B 1, то 50 результат, полученный от деления числа

А, равный А (с(-,, d.,..., д ) сравнивается с нулем в блоке б конца деления. Если A=O то результат деления числа A иа В снимается в виде С =

56

Елее A/Â = (C,,C,...,C; ..., C > ) с сумматора 7. Если же АФО, то AÀ посылается в сумматор 7, в котором оно либо вычитается, либо складывается с первоначальным содержимым сумматора 7 в зависимости от сигнала с блока 11 режима® работы сумматора. После первой итерации всегда происходит сложение с предшествующим сбросом в нуль сумматора 7. При этом получают произведение А . В в бло1 ке 8 умножения, 55

В блоке 10 анализа произведения осуществляется сравнение полученного произ1 Ф ведения A В со значением А, в качестве которого на первой итерации выступает само А и на последующих A. Блок 9 вычитания вычисляет значение нового делимого А по формуле

1 И

А= A.Â вЂ” A если AВ) A", и

A=A В AÀ + P

1 если А В (A".

Блок 11 режима работы сумматора при А ° В> А запоминает сигнал вычиI тания, а при A.B(A-сигнал сложения для следующей итерации. Новое делимое с выхода блока 9 вычитания поступает на вход блока 4 вычисления итерации.

С этого момента начинает я вторая итерация деления (аналогичная описанной выше) . Процесс деления продолжается до тех пор пока не получится значение

А=О.

Таким образом, предложенное устройство обеспечивает возможность создания принципиально нового семейства ЭВИ, работающих в системе остаточных классов, что позволяет увеличить быстродействие операции деления по сравнению с устройствами, работающими в позиционных системах из-за независимой поразрядной обоаботки данных.

Формула изобретения

Устройство для деления, содержащее регистр делимого, регистр делителя и сумматор, о т л и ч а ю щ е е с я тем, что,с целью повышения быстродействия, в устройство. введены блок выбора элементарного делителя, блок умножения, блок вычитания, блок анализа произведения, блок конца итерации, блок конца деления, блок режима работы сумматора, блок вычисления итерации; причем восход регистра делимого подключен к первому входу блока вычисления итерации, второй вход которого подключен к шине позиционного признака делимого; выход регистра делителя подключен ко входу блока выбора элементарного делителя, к третьему входу блока вычисления итерации и к первому входу блока умножения, выход блока элементарного делителя подключен к четвертому входу блока вычисления итерации, пятый вход которого подключен к шине позиционного признака делителя и ко второму входу блока умножения, третий вход которого подключен к первому входу сумматора, первому входу блока вычитания, первому входу блока конца деления, к выходу блока вычисления итерации и ко входу блока конца итерации, выход которого подключен ко вто579614

Составитель В. Жуков

Техред С.Беца корректор М.Демчик

Редактор Л. Утехина

Заказ 4396)45 Тираж 818 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, r. Ужгород, ул. Проектная, 4 рому входу блока конца деления и к шестому входу блока вычисления итерации; выход блока конца деления подключен к четвертому входу блока умножения, к первому входу блока анализа произведения, ко второму входу блока вычитания и ко второму входу сумматора; выход блока умножения подключен ко второму входу блока анализа произведения, выход которого подключен через блок режима работы сумматора к третьему входу блока вычитания, выход которого подключен к седьмому входу блока вычисления итерации. Выход сумматора соединен с выходом устройства.

Источники информации, принятые в внимание при экспертизе:

1. Патент Франции 2241384, кл. t 06 F 7/00, 03.08.74.

Патент Франции 2170695, кл . 6 06 F 7/00, 30.01.71.