Устройство для умножения

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

Союз Соатьтскик

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву

{22) Заявлено 02.12.75 (21) 2195576/18-24 (51) М. Кл.

G 06 F 7/39 с присоединением заявки №вЂ”

{23) Приоритет

{43) Опубликовано051177 Бюллетень № 41

{45) Дата опубликования описания 29,11.77

Г14РДЬРЬт4414ЯЬ 14а1тЬт

6141Т1 МЬЬЬЬТрЬЬ GGGP

14 ДЬЬЬИ ЬзобРЬТ4114

1 ЬТЬРЫТЬй (53) УДК

681.325(088.8) (72) Авторы изобретения

А. Л. Рейхенберг и P. Я. Шевченко

Pl) Заявитель (54) УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ

ТО

Изобретение относится к области цифровой вычислительной техники и может найти применение для аппаратной реализации операции умножения в различных системах автоматики, управления, измерения и контроля.

Йзвестно двоичное устройство деления, содержащее дна одноразрядных сумматора-вычитателя, три регистра сдвига, блок формирования констант, блок анализа знака, блок анализа сходимости, блок сброса и блок управления j 1).

В таком устройстве невозможно выпол-)5 нение операции умножения.

Наиболее близким решением к изобретению является специализированное арифметическое устройство, содержащее пер- 20вый и второй регистры сдвига, выходы которых соответственно соединены со входами первого и второго суммато-, ров-вычитателей, BbIxo которых соответственно соединены со входами этих 25 регистров сдвига. Выход третьего регистра сдвига соединен со вторым входом первого сумматора-вычитателя (2).

Такое устройство имеет недостаточное быстродействие. 30

Целью изобретения является повышение быстродействия.

Цель достигается тем, что предложенное устройство дополнительно содержит блок анализа сходимости, блок фор.мирования констант и блок управления, вход которого соединен с первым выходом блока анализа сходимости, второй выход которого соединен со входами управления сумматоров-вычитаФелей. Второй выход второго регистра сдвигИ соединен со входом блока анализа сходимости. Выход третьего регистра сдвига соединен со своим входом. Выход блока формирования констант соединен со вторым входом второго сумматора-вычитателя, а выходы блока управления — с управляющими входами регистров сдвига и входом блока формирования констант.

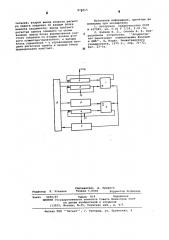

На чертеже представлена структурная схема устройства для умножения.

Устройство содержит одноразрядные сумматоры-вычитатели 1 и 2 комбинационного типа, регистры сдвига 3-5, блок формирования констант 6, блок анализа сходимости 7 и блок упраэления 8.

Выходы первого и второго регистров сдвига 3 и 4 соединены с первыми входами сумматоров-вычитателей 1 и 2 со"57,9б15 щ Х>О лРи Х1 CO ответственно. Выходы которых соединены соответственно со входами этих регистров, выход третьего регистра сдвига 5 соединен со своим входом и вторым входом сумматора-вычитателя 1 . На вто5 рой вход сумматора-вычитателя 2 подсоединен выход блока формирования констант. Второй выход регистра сдвига 4 соединен со входом блока анализа сходимости, первый выход которого соединен со входом блока управления, а вто10 рой — со входами управления сумматороввычитателей 1 и 2. Выходы блока управления соединены с управляющими входами регистров сдвига 3-5 и входом блока формирования констант.

В качестве блока формирования констант вида 2 1 может быть использовано одностороннее запоминающее устрой ство или рециркуляционный регистр сдвига с логическим управлением . 20

Блок анализа сходимости предназначен для анализа сходимости процесса вычисления и определения на каждой итерации очередной цифры псевдочастного q . Блок анализа сходимости со- 25

j держит цифровую схему сравнения, два триггера и логические элементы.

Блок управления содержит генератор тактовых сдвигающих импульсов, счетчик и логические элементы. 30

Входами устройства для умножения являются входы ячеек разрядов регистра сдвига 4 для сомножителя Х и входы ячеек разрядов регистра сдвига 5 для сомножителя У. Выходом устройства являются выходы ячеек разрядов регистра сдвига 3.

Процесс операции умножения основан на одновременном решении системы разностных рекуррентных соотношений, например, для двоичной системы счисле ния:

Цикл вычисления выполняется итерационным путем и состоит из п +1 итераций, где и -число разрядов одного из сомножителей. Каждая итерация вычисляется последовательно за п + п тактов, где rn — число дополнительных разрядов для компенсации погрешности усечения чисел при сдвиге. бО

Устройство работает следующим образом.

Первоначально в регистр сдвига 3 заносится нулевое значение, в регистр сдвига 4 — значение сомножителя Х, в 65

Регистр сдвига 5 — значение сомножителя У. В любой итерации с выхода блока управления выдается серия тактовых сдвигающих импульсов для сдвига содержимого регистра сдвига 5, а также продвижения содержимого регистров сдвига 3 и 4 Н подачи очередной константы вида 2 из блока формирования констант на входы сумматоров-вычитателей 1 и 2.

Результаты каждой итерации записываются с выходов сумматоров-вычитателей 1 и 2 младшими разрядами вперед в освобождающиеся при сдвиге старшие разряды регистров сдвига 3 и 4 и продвигаются в сторону младших разрядов.

В конце каждой итерации определяется очередная цифра o, . При q, = 1 суммаФ тор-вычитатель 1 работает в режиме сложения, а сумматор-вычитатель 2

В режиме вычитания, при о „ = -1 соответственно в режиме вычитания и сложения. П сле выполнения и +1 итераций или при равенстве содержимого регистра сдвига 4 нулю в регистре сдвига 3 находится значение произведения Ху. Для подавляющего большинства значений сомножителей итерационный процесс сходится на итерации, номер которой меньше n . .В этом случае с первого выхода блока анализа сходимости выдается сигнал останова, и блок управления перестает выдавать тактовые сдвигающие импульсы на следующей итерации. Благодаря асинхрон-. ному режиму работы быстродействие устройства повышается примерно вдвое

Максимальное время выполнения операции умножения в тактах равно

Т< п(а+4) Увеличение быстродействия достйгается за счет применения блока анализа сходимости процесСа.

Формула изобретения

Устройство для умножения, содержащее первый и второй регистры сдвига, выходы которых соответственно соединены со входами первого и второго cvMматоров-вычитателей, выходы которых соответственно соединены со входами этих регистров сдвига, выход третьего регистра сдвига соединен со вторым входом первого сумматора-вычитателя, о тл и ч а ю щ е е с я тем, что, с целью повышения быстродействия, оно содержит блок анализа сходимости, блок формирования констант и блок управления, вход которого соединен с первым выходом блока анализа сходимости, второй выход которого соединен со входами управления сумматоров-вычи57)615

Составитель В. Кривяго

Техред С.Беца Корректор М.Деглчик

Редактор Л. Утехина

Заказ 4396/45 Тираж 818

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4 тателей; второй выход второго регистра сдвига соединен со входом блока анализа сходимости; выход третьего регистра сдвига соединен со своим входом; выход блока формирования констант соединен со вторым входом второго сумматора-вычитателя, а выходы блока управления — с управляющими входами регистров сдвига и входом блока

:формирования констант.

Источники информации принятые во внимание при экспертизе:

1. Авторское свидетельство СССР

9 497585, кл. 6 06 F 7/39, 2.01.74.

2. Байков В. Д., Смолов В. Б. Операционное устройство. Anrrapатурная реализация элементарных функций в ЦВМ, Л., Издат. Ленинградского университета, 1975 г., стр. 71-72, фиг. 22-5а.