Процессор управляющей вычислительной машины

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (11) 579621 (6l) Дополнительное к авт. свид-ву— (22) Заявлено 17.1275 (21) 2300408/18-24 с присоединением заявки № (23) Приоритет (43) Опубликовано 051177 Бюллетень ¹41 (45) Дата опубликования описания 30»7, (51) М. Кл.

G 06 1 15/00

Гэит114рЭтээииыи иэаитэт

Вэиэтэ Миииитрэи OCCAM

44 Диииа ИЗЭЭРЭТЭИИЭ и Этирытий (53) УДК681. 325 (088.8) (72) Авторы К.Н. Белоусов, В.Н. Белый, Э.В. Купченко, МЗОбрЕтЕИИя Н.В.Плахотный, К.Г. Самофалов и lu,в. Щербин:, (7l) 3aÿâìòeëü

Киевский ордена Ленина политехническии институ. им. 50-летия Великой Октябрьской социалистическ<.й революции (54} ПРОЦЕССОР УПРАВЛЯЮЩЕЙ ВЫЧИСЛИТЕЛБНОИ

МАШИНЫ

15

Изобретение относится к вычислительной технике и может быть использовано в управляющих вычислительных комплексах.

Известно устройство защиты памяти, содержащее ари@метико-логический блок и регистры для запоминания граничных адресов совокупности ячеек памяти, в котором адресная часть запроса и памяти сравнивается с этими граничными адресами и, в зависимости от результатов сравнения, доступ к памяти разрешается или запрещается11), Однако в этом устройстве необходимы дополнительные регистры для запоминания граничных адресов памяти.

Наиболее близким к изобретению по технической сути является входящий в набор агрегатных модулей ACBT-M процессор управляющей вычислительной машины М-6000, содержащий регистр фоамнрования фаз выполнения операций,регистр текущего адреса, регистр номе.:ра команды, регистр кода операций, устройство защиты памяти, входы-выходы которых подключены к соответствующим выходам-входам арифметико-логического устройства (2).

Однако в этом устройстве не осуществляется защита постоянных программ от ошибочного к ним обращения.

Целью изобретения является повышение надежности работы про тессора.

Для этого в процессор дополнительно введены элементы ИЛИ, два элемента И, элемент НЕ, первый дешифратор и второй дешифратор, вход котopoqp подключен к выходу регистра кода операцийт а выход — к первому входу первого элемента И, второй вход которого подключен к выходу старшего разряда регистра номера команды и к первому входу второго элемента И, второй вход которого соединен с выходом старшего разряда регистра текущего адреса, а третий — через первый инвертор и первый дешифратор подключен к выходу регистра формирования фаз выполнения операций, выходы первого и второго элементов И подсоединены к входам элемента ИЛИ, выход которого подключен устройству защиты памяти.

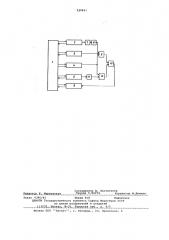

На чертеже изображена блок-схема процессора управляющей вычислительной машины.

Процессор содержит арифметико-логическое устройство 1, регистр 2 формирования фаз выполнения операций, 579621 регистр 3 текущего адреса, регистр 4 номера команды, регистр 5 кода операций, устройство 6 защиты памяти, дешифратор 7, элемент НЕ 8, элемент

И 9, элемент ИЛИ 10, дешифратор 11 и элемент И 12.

Процессор работает следующим обра.зом.

Оперативное запоминающее устройство, с которым процессор обменивается информацией, состоит из двух равных

10 областей. Адреса ячеек памяти первой и второй области различаются по значению старшего двоичного разряда номера ячейки. В первой области ОЗУ размещаются постоянные программы, защищаемые от ошибочного к ним обращения.

Вторая область ОЗУ отводится для размещения сменных программ. Если процессор выполняет адресную команду, расположенную во второй области оперативного запоминающего устройства и осуществляет ошибочное обращение по адресу к первой области запоминающего устройства, то появляются сигналы на прямом выходе триггера старше- 25 го разряда регистра 4 номера команды и на инверсном выходе триггера старшего разряда регистра 3 текущего адреса. Эти сигналы присутствуют на двух входах элемента И 9. 30

Если при этом процессор находится не в фазе прерывания,т.е.на выхо дах регистра 2 формирования фаз выполнения операций и соответственно на входах дешифратора 7 отсутствует д комбинация сигналов, соответствующая фазе прерывания, то отсутствует сигнал на выходе дешифратора, и после элемента НЕ 8 присутствует сигнал на третьем входе элемента И 9. 40

Наличие сигналов на всех входах элемента И 9 обуславливает появление сигнала на выходе этого элемента,который через элемент ИЛИ 10 поступает на вход устройства 6 защиты памяти.

В результате устройство 6 запрещает обращение к первой области памяти, прерывает исполнение текущей сменной программы, содержащей ошибочное обращение, и осуществляет передачу управления команде, записанной в ячейке памяти с фиксированным адресом, соответствующим причине прерывания.

Аналогично осуществляется защита первой области памяти от выполнения некоторых запрещенных безадресных 55 команд, содержащихся в сменных программах.

К таким командам относятся..каманды установки и снятия масок, Оста- . нов и другие, исполнение которых может нарушить содержимое первой области памяти. При наличии на выходах триггеров регистра 5 кода операции и соответственно на входах дешифратора 11 одного из кодов запрещенной операции на выходе дешифратора 11 появляется сигнал, поступающий на один из входов элемента И 12. Сигнал с прямого выхода триггера старшего разряда регистра номера команды поступает на второй вход элемента И

12. Этот сигнал появляется во всех случаях, когда подлежащая исполнению команда размещена во второй области памяти. Наличие сигналов на двух входах элемента И 12 обуславливает появление сигнала на ее выходе. Этот сигнал через элемент ИЛИ 10 поступает на вход устройства защиты памяти б ф зрмула изобретения

Процессор управляющей вычислительной машины, содержащий регистр формирования фаз выполнения операций, регистр текущего адреса, регистр номера команды, регистр кода операций, устройство защиты памяти, входы-выходы которых подключены к соответствующим выход 1м-входам арифметико-логического устройства, о т л и ч а юшийся тем, что, с целью повышения надежности работы процессора, в него дополнительно введены элемент

ИЛИ, два элемента И, элемент НЕ,первый дешифратор и второй дешифратор, вход которого подключен к выходу регистра кода операций, а выход — к первому вход первого элемента И, второй вход которого подключен к выходу старшего разряда регистра номера команды и к первому входу второго элемента И, второй вход которого goeдинен с выходом старшего разряда регистра текущего адреса, а третий через первый инвертор и первый дешифратор подключен к выходу регистра формирования фаз выполнения операций, выходы первого и второго элементов И подсоединены к входам элемента ИЛИ, выход которого подключен к устройству защиты памяти.

Источники информации, принятые во внимание при экспертизе:

1. Патент франции Ф 2027419 кл. G 06 F 9/00, 12.12.1969.

2. Архитектура М-6000, НИИУВМ, Северодонецк, 1972.

579621

Составитель В. Евстигнеев

Техред З.Фанта Корректор М.Демчик

Редактор И. Марховская

ñ с с с

Филиал ППП Патент, г. Ужгород., ул. Проектная, 4

Заказ 4396/45 Тираж 818 Подписное

ЦНИИПИ 1осУдарственного комитета Совета Министров СССР по делам изобретений и открытий

113035 Москва Ж-35 Ра шская наб. д. 4 5