Запоминающее устройство

Иллюстрации

Показать всеРеферат

ОГ1ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

1п 580584

Союз Советских

Социалистических

Республик (61) Дополнительное к авт. свид-ву (22) Заявлено 28.06.76 (21) 2377591/24 (51) М. Кл, С 11С 11/00 с присоединением. заявки №

Государственный комитет

Совета Министров СССР (23) Приоритет (43) Опубликовано 1,5.11.77. Бюллетень № 42 (45) Дата опубликования описания 28.10.77 (53) УДК 681.327(088.8) ло делам изобретений и открытий (72) Авторы изобретения

Ю. Н. Мартыненко и Я. Ш. Безродный (71) Заявитель (54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

Изобретение относится к запоминающим устроиствам и может OblTb использовано в качестве оперативнои памяти.

Одно из известных запоминающих устройств содержит несколько блоков оперативнои памяти, каждыи из которых имеет блок местного управления, входы приема кода адреса, кода числа и запроса, накопитель и выходной коммутатор, входами соединенный с выходами накопителя, а выходами — с выходными кодовыми шинами числа (1). Однако известное устрой ство способно оослуживать лишь один канал, что, во-первых, ограничивает его функциональные возможности, а, вовторых, ве позволяет в пол ной мере реализовывать возможность повышения скорости вычислительного процесса, связанного с применением оперативной памяти с расслоением.

Наиболее близким к изобретению технически м решением является запоминающее устройство, содержащее выходные шины, nm-канальных блоков оперативной памяти, каждый из которых содержит накопитель, входы которого подключены к одним выходам соответствующего блока управления, а,выходы через элементы И вЂ” ко входам соответствующего коммутатора (2). В этом из|вестном устройстве используется большое количество выходных шин и большой объем оборудования коммутаторо в, что существенно .усложняет его, по вышает стоимость, а также снижает надежность.

Целью изобретения является упрощение и повышение падеж ности. В описываемом уст5 ройстве это достигается тем, что оно содержит m-разрядный регистр, приоритетный блок, nm дополнительных элементов И и п элементов И 1И, выходы которых подключены к одним из входов соответствующих элементов И, 10 а входы — к выходам соответствующих дополнитель|ных элементов И, входы m-разрядного регистра соединены с первыми входами дополнительных элементов И и другими выходами соответствующих блоков управления, 15 выходы т- разрядного регистра через лриоритетный блок подключены ко вторым входам соответствующих дополнительных элементов

И и,выходам устройства.

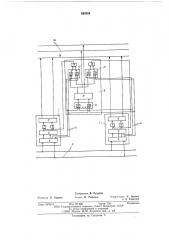

На чертеже представлена блок-схема опи20 сываемого устрой|ства.

Оно содержит и блоков 1 оперативной памяти, каждый из которых содержит блок 2 управления, имеющий т групп входов приема кода адреса, кода числа и запроса, соединен25 .ных с соответствующими входными шинами

3 (пг — количество входных ка|налов), пг выходов 4 (для ответа на обслуживание выбранного канала), накопитель 5, коммутатор 6, элементы И 7, блок 8 управления коммутато30 рами, содержащ ий m-разрядный регистр 9, 580584 имеющий а входов .на разряд 10, т-входовый приоритетный блок 11, и rpyinn 12 по т дополнительных элементов И 13, шины 14 ответа на обслужи ва ние, и элементов ИЛИ 15 и выходные числовые шины 16, Выходы элементов ИЛИ 15 подключены к одним из входов соответствующих элементов И 7, а входы— к выходам соответствующих дополнительных элементов И 13, входы регистра 9 соединены с первыми входами элементов И 13 и выходами 4 блоков 2, выходы регистра 9 через блок

11 подключены ко вторым входам соответствующих элементов И 13 и ши нам 14, являющимся выходами устройства, При записи информации каждый блок 1 работает независимо от других, п ри нимает код адреса и числа и передает на шины 14 ответ на обслуживание. При считывании инфор мацни одновременно из нескольких блоков 1 (соответственно в несколько различных каналов), каждый из блоков 1 принимает,код адреса и запрос из входных шин 3, вырабатывает ответ на обслуживание на выходах 4 блока 2 и выдает выходную информацию из .накопителя 5 на входы элементов И 7. Далее блок 8 управления коммутаторами подключает коммутато.ры 6.к шинам 16 в требуемой последовательности. Ответы на обслуживание с выходов 4 блока в 2,поступают на входы разрядов 10 .регистра 9 и запоминаются в нем. Блок 11 анализирует состояние регистра 9 и вырабатывает на соответствующем выходе сигнал, соответствующий ответу на входе регистра 9, имеющем более высокий приоритет. Этот сигнал передается на шины 14 и поступает на входы элементов И 13. При этом открывается один из элементов И 13 той группы 12, которая соответствуетвыбранномув данный момент блоку 1.

Сигнал с выхода элемента И 13 через элемент

ИЛИ 15 поступает на входы элементов И 7 выбранного в данный момент коммутатора,6, чем обеспечивается передача информации из на копителя 5 к шинам 16. После этого данный блок 1 оперативной памяти готов к приему очеред ного запроса. Далее блок управления коммутаторами 8 производит передачу на выходные шины 16 информации от остальных

4. блоков 1 оперативной памяти в соответствии с приоритетом.

Технико-экономический эффект выражается в том, что при использовании описываемого устрой ства, во-первых, сокращается количество,выходных шин в т раз по сравнению с известным (2) и, во-вторых, соответственно сокращается количество оборудования коммутаторов 6, которые B описываемом устройстве

10 выполнены одноканальными, вместо т-канальных, Это приводит к существенному сокращению объема оборудования устройства и повышению его надежности при сохранении быстродействия и функциональных возмож15 ностей.

Формула изобретения

Запоминающее у|стройство, содержащее nm20 канальных блоков оперативной памяти, каждый из которых содержит накопитель, входы которого подключены к одним выходам соответствующего блока управления, а выходы через элемен1ы И вЂ” ко входам соответствую25 щего коммутатора, о т л и ч а ю щ е е с я тем, что, с целью упрощения и повышения надежности устройства, оно содержит т-разрядный регистр, приоритетный блок, nm дополнительных элементов И и и элементов ИЛИ, выходы

30 которых подключены к одним из входов соответствующих элементов И, а входы — к выходам соответствующих дополнительных элементов И, входы m-разрядного регистра соединены с первыми входами донолнительных

35 элементов И и другими выходами соответствующих блоков управления, выходы т-разрядного регистр а через приоритетный блок подключены ко вторым входам соответств ующих дополнительных элементов И и выходам

40 устройства.

Источники информации, принятые во внимание при экспертизе

1. Шигин А. Г. и Дерюгин А, А. Цифровые вычислителыные машины (память ЦВМ). М., 45 «Энергия», 1975,,с. 495.

2. Патент Великобритании Мю 1069480, кл, G 4А, 1967.

á80584

Редактор Л. Тюрина

Заказ 2470/14 Изд. № 900 Тираж 738

НПО Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Подписное

Типография, пр. Сапунова, 2

Составитель В. Рудаков

Техред Н. Рыбкина

1(оррскторы: Л. Орлова и 3. Тарасова