Устройство для защиты памяти

Иллюстрации

Показать всеРеферат

(») 580586

ОПИСАН И Е

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Сова Соввтских Социалистических

Республик (61) Дополнительное к авт. свид-ву (22) Заявлено 17.05.76 (21) 2361296 24 с присоединением заявки № (23) Приоритет (43) Опубликовано 15.11.77. Бюллетень № 42 (45) Дата опубликования описания 28.10.77

Государственный комитет

Совета Министров СССР т1о делам изобретений и открытий (53) УДК 681,327(088.8) (72) Авторы изобретения

М. Н. Бобов и А, A. Обухович (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ЗАЩИТЫ ПАМЯТИ

Цель изобретения заключается в повышении надежности. В описываемом устройстве это достигается тем, что оно содержит триггер и дополнительный элемент И, один вход которого подключен к выходу блока регистрации адреса, другой вход — к выходу триггсра, а выход дополнительного элемента И соединен с щи ной разрешения обращения к памяти, первый вход триггера подключен к адресным шинам, а второй — к выходу блока сравнения.

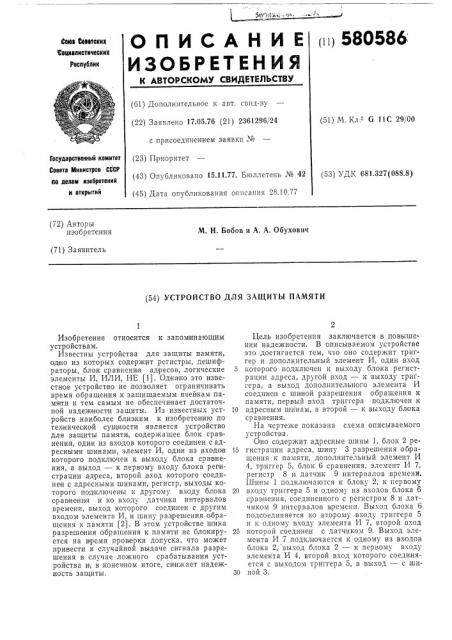

На чертеже показана схема описываемого устройства.

О но содержит адресные шины 1, блок 2 регистрации адреса, шину 3 разрешения о6ращения к памяти, дополнительный элемент И

4, триггер 5, блок 6 сравнения, элемент И 7, регистр 8 и датчи к 9 интервалов времени.

Шины 1 подключаются к блоку 2, к первому входу триггера 5 и одному из входов блока 6 сравнения, соединенного с регистром 8 и датчиком 9 интервалов време и. Выход блока 6 подсоединяется ко второму входу триггера 5 и к одному входу элемента И 7, второй вход которой соединен с датчиком 9. Выход элемента И 7 .подключается к одному из входов блока 2, выход блока 2 — к первому входу элемента И 4, второй вход которого соединяется с выходом триггера 5, а выход — с шиной 3, Изобретение относится к запом|инающим устройствам.

Известны устройства для защиты памяти, од но из которых содержит регистры, дешифраторы, блок сравнения адресов, логические 5 элементы И, ИЛИ, НЕ (1). Однако это известное устройство не позволяет ограничивать время обращения к защищаемым ячейкам памяти и тем самым не обеспечивает достаточной надежности защиты. Из известных уст- 10 ройств наиболее близким к изобретению по технической сущности является устройство для защиты памяти, содержащее блок сравнения, один из входов которого соединен с адресными шинами, элемент И, один из входов 15 которого подключен к выходу блока cpaiameния, а выход — к первому входу блока регистрации адреса, второй, вход которого соединен с адресными шинами, регистр, выходы которого подключены к другому входу блока 20 сравнения и ко входу датчика интервалов време ни, выход которого соединен с другим входом элемента И, и шину раз)решения обращения к памяти (2). В этом устрой стве шина разрешения обращения к памяти не блокиру- 25 ется на в|ремя проверки допуска, что может привести к случайной выдаче сигнала разрешения в случае ложного срабатывания устройства и, в конечном итоге, снижает надежность защиты, 30 (51) М. Кл.- G 11С 29/ 00

580586

Формула изобретения

Составитель В. Рудаков

Техред H. Рыбкина

1(орректоры: Л. Орлов» и 3. Тарасова

Редактор Л. Тюрина

Заказ 2470/16 Изд. л1 900 Тираж 738

НПО Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Подписное

Типография, пр. Сапунова, 2

По шине 1 код адреса ячейки памяти, к которой п роизводится обращение, поступает в блоки 2 и 6. По этому же сигналу триггер

5 устанавливается в нулевое состояние и закрывает элемент И 4. Блок 6 сравниваетпришедший код адреса с кодами адресов, записанными в регистре 8. При совпадении кодов адресов блок 6 сравнения запускает датчик 9 интервалов времени, открывает элемент И 7 и устанавливает триггер 5 в единичное состо яние. Датчик 9 формирует време иной интервал, соответствующий пришедшему коду адipeca, который через открытый элемент И 7по ступает в блок 2. Блок 2 через открытый элемент И 4 по ши не 3 выдает сигнал .разрешения обращения к запрашиваемой ячейке памяти в течение сформированного интервала времени. Если же сравнения адрссов в блоке

6 сравнения не прои сходит, то разрешение по шине 3 не выдается.

Таким образом, в описываемом устройстве в отличие от известного надежность защиты повышается, так как выдача сигнала разре:шения по шине 3 в момент прихода адреса запрещается до тех пор, пока не происходит сравнен ия его с кодом адреса, записанным в регистре 8, т. е. пока блок 5 не выдает сиг нала, разрешающего допуск к запраши ваемой ячейке памяти.

Устройство для защиты памяти, содержащее блок сравнения, один из входов которого соединен с адресными шинами, элемент И, один из входов которого подключен к выходу блока сравнения, а выход — к первому входу блока регистрации адреса, второй вход которого соединен с адресными шинами, регистр, 10 выходы которого подключены к другому входу блока сравнения и ко входу датчика интервалов.времени, выход которого соединен с другим входом элемента И, и шину разрешения обращения к памяти, от л и ч а ющ е е с я

15 тем, что, с цель ю повышения надежности устройства, оно содержит триггер и дополнительный элемент И, один вход которого подключе н к выходу блока регистрации адреса, другой вход — к выходу триггера, а выход

20 дополнительного элемента И соединен с шиной разрешения обращения к памяти, первый вход триггера под ключен к адресным шинам, а второй — к выходу блока сра внения.

И сточн ики и|нформации, 25 принятые во внимание при экспертизе

1. Патент США Юю 3473159, кл. G 06F

1/00, 1969.

2; Авторское свидетельство Хо 397964, кл.

G 11С 7/00, 1970.