Постоянное запоминающее устройство

Иллюстрации

Показать всеРеферат

". c((.c, . гмте;11 и

ОП ИСАН

ИЗОБРЕТЕН

К АВТОРСКОМУ СВИДЕТЕЛЬ

Р Ц ( р МБА

Союз Советских

Социалистимеских

Республик

) 581508 (61) Дополнительное к авт. свид-ву (22) Заявлено 03.09.75 (21) 216977 с присоединением заявки № (23) Приоритет (43) Опубликовано25, 11,77 Бюллет (45) Дата опубликования описания

1) М. Кл, (11 С 17/00

Государствеиие1й комитет

Совета Министров СССР оо делам изооретений и открытий

3) УДК 681 327 66 (088.8) (72) Авторы изобретения

А. М. Сепией и Д. С. Тростяненкий

Киевския ордена Трудового Красного Знамени завод электронных вычислительных и управлнюших машин (71) Заявитель (54) ПОСТОЯННОЕ ЗАПОМИНАЮШЕЕ УСТРОЙСТВО

Изобретение относится к области вычислительной техники и может быть использовано при построении устройств хранения дискретной информации.

Известны постоянные запоминающие устройства (ПЗУ), содержащие числовые матрицы и дешифратор (1) и (2) .

Одно из известных ПЗУ содержит числовые матрицы, соединенные с регистром числа, и блок выдачи информации. Недостатком устройства является малая информационная емкость (1)

Наиболее близким техническим решением к данному изобретению является ПЗУ, которое содержит, как и предложенное, числовые матрицы, соединенные с регистром числа, выходы которого подключены к первым входам блока выдачи информации, и дешифратор номера числовых матриц (2).

Недостатком устройства является сравнительно небольшая емкость, обусловленная использованием накопителя, состоящего из одной числовой матрицы. Однако при большой емкости накопитель постоянного запоминающего устройства обычно состоит из нескольких числовых матриц. Это требует введения регистра числа на каждую числîBóâ матрицу, увеличения числа входов блока выдачи информации, что приводит к увеличению оборудования.

Цель извбретения — повышение информационной емкости ПЗУ.

Указанная цель достигается тем, что устройство содержит элементы И по количеству числовых матриц и на каждый разряд числовой матрицы элемент ИЛИ, выходы элементов ИЛИ подключены ко вторым входам блока выдачи информации, а входы соединены с выходами элементов И, первые входы элементов И подключены к дешифратору номера числовых матl0 pHLl,, а вторые входы — к соответствующим входам устройства.

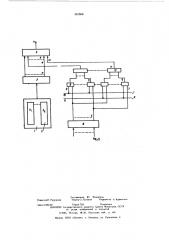

На чертеже дана принципиальная схема

ПЗУ.

ПЗУ содержит накопитель 1, состоящий из q числовых матриц 2, подключенных к регистру

3 числа. Выходы регистра 3 подключены к первым входам 4 блока 5 выдачи информации.

Выходы дешифратора 6 номера числовых матриц подключены к первым входам 7 элементов

И 8. В устройстве содержится п групп (по числу

20 разрядов слова) по q элементов И 8 в группе.

В зависимости от вида хранимой информации вторые входы 9 элементов И 8 подключены к соответствующим входам устройства: к шине

10 логической «1» или к шине 11 логического

«О». Выходы элементов 8 подключены к элемен58 508 там ИЛИ 12, количество которых равно числу разрялов и. Выхолы элементов ИЛИ 12 соелинены со вторыми вхолами 13 блока 5 выдачи информации. Блок 5 выдачи информации содержит п пар входов 4 и 13.

В кажлой числовой марице 2 информация представлена поразрядно в прямом или обратном коде в зависимости от того, преобладают ли в данном разряде нули или единицы соответственно. Пусть в числовой матрице 2 с номером

«1» в первом, втором и пятом разрядах количество нулей больше количества единиц, а в остальных разрядах, наоборот, преобладают единицы. Тогда в матрице 2 в первом, втором и пятом разрядах информация занесена в прямом коле, а в остальных разрядах — в обратном коде. В числовой матрице 2 с номером « », например, в разряде п преобладают единицы.

Этот разряд занесен в обратном коде.

Для выдачи информации из блока 5 в прямом коде выполнено соответствующее подключение входов 9 элементов И 8 к шинам 10 и I.

Для рассматриваемого примера входы 9 элементов И 8 подключены; для первого, второго и пятого разрядов элементов И 8, соответствующих числовой матрице 2 с номером «1», к шине

lO логической «I», остальные входы 9 элементов И 8 подключены к шине! 1 логического «О»; для разряда и элемента И 8 вход 9 подключен к шине 11, в остальных разрядах элементов

И 8 входы 9 соединены с шиной 10.

Устройство работает следующим образом.

Пусть выбирается информация из числовой матрицы 2 с номером «1». В регистр 3 в первом, втором и пятом разрядах информация записывается.в прямом коде, а в остальных разрядах — в обратном коде. На выходах элементов

ИЛИ 12, соответствующих разрядам I, 2, 5, появляются сигналы, управляющие выдачей информации из блока 5 прямым кодом, на остальных выходах элементов ИЛИ 12 сигналы отсутствуют. Это означает, что из блока 5 в остальных разрядах будут выланы обратные коды.

При чтении информации из q-ой числовой матрицы 2 на выхолах элементов ИЛИ 12, соответствующих разряд м от до (и — 1), появляются сигналы, управляющие выдачей информации в прямом коде. На выходе элемента

ИЛИ 12, соответствующего и-му разряду, сигнал отсутствует, этот разряд из блока 5 выдачи информации выдается в обратном коде.

Формула изобретения

11

Постоянное запоминающее устройство, содержащее числовые матрицы,. соединенные с регистром числа, выходы которого подключены к первым входам блока выдачи информации, и дешифратор номера числовых матриц, отяичаюи!ееся тем, что, с целью повышения информационной емкости устройства, оно содержит элементы И о количеству числовых матриц и на каждый разряд числовой матрицы элемент

ИЛИ, выходы элементов ИЛИ подключены ко у вторым входам блоки выдачи информации, а входы соединены с выходами элементов И, первые входы элементов И подключены к дешифратору номера числовых матриц, а вторые входы — к соответствующим входам устройства.

Источники информации, принятые во внима36 ние при экспертизе:

1. Брик Е. А. Техника ПЗУ, «Советское радио», 1973, с, 96.

2. Авторское свидетельство СССР № 483712, кл. G I! С 17/00, 02.01.73.

581508

Составитель К). Розенталь

Техред О. Луговая Корректор А. Кравченко

РедакторН. Разумова

Филиал !1Г1Г1 «Г1атентэ, г. Ужгород, ул. Проектная,. 4

Заказ 4584/40 Тираж 729 Г!одписное

LlHHHtlH Государственного комитета Совета Министров СССР по делам изобретений и oTKpblTHA

I! 3035, Москва, Ж-35, Раугнская наб., д. 4/5