Устройство цикловой синхронизации

Иллюстрации

Показать всеРеферат

I :

GllNCAHNK

ИЗОБРЕТЕН ИЯ

Союз Советских

Сеэцфб&лмстмчя аких

1эвспублни (11)581591

И АВТОРСКОМУ СВИДН ИЛЬСТВУ (! (61) Дополнительное к авт. саид-ву (22) Заявлеьз 03,12.78 (21) 1 с д 00 80 .е присоединением заявки №„ (51) М. Кл.

Н 04 L7/08

Гасударственный намнтет

Фааета Мнннатрав СССР аа делам нэааретеннй н аткрытнй (23) Приоритет (43) Опубликовано 25.11.77. Бюллетень ¹43 (ГЗ) УДК 621,394. .662 (088.8) (45) Дата опубликования описания 22.42.77

{72) Автсры изобретения

И. Г, Маркатун, И. И. Храмов, В. Г. Подовннко и З.А. Вартапетов

Институт кибернетики АН Азероаиджанской ССР (71) Заявитель (54) УСТРОЙСТВО ЦИКЛОВОЙ СИНХРОНИЗАЦИИ

Изобретение относится к передаче данных и может использоваться в синхронных помехозащнщенных системах передачи данных по каналам связи.

Известно устройство цнкловой синхрониза- к цнн, содержащее последовательно соединенные формирователь стробирующих импульсов, опознаватель маркериого сигнала и блок управления, выход которого соединен с входами тактового распределителя непосредственно и через делитель частоты, а также индикатор состояния щ синхронизма f1).

Однако известное устройство обладает низкой помехоустойчивостью приема при сел.акции синфазирующего импульса по длительности.

Цель изобретения — повышение помехоустойчивости устройства. !

Для этого в устройство цикловой синхрони- зации, содержащее последовательно соединен- ные формирователь стробируюших импульсов, опознаватель маркерного сигнала н блок управчення, выход которого соединен с входами такгового распределителя непосредственно н через делитель частоты, а также индикатор состояния синх1гонизма, введены два tpHrrepa, трн блока задержки, блок совпадения и дифференцирую- . щий блок, прн этом выход оебзнавателя маркерного сигнала нодключеи к входу первого блока задержки, выход которого соединен через первый триггер с первым дополнительным входом блока управления, а через последовательно соединенные второй триггер, блок совпадения н второй блок задержки — к другому входу первого триггера, выход которого подключен к второму дополнительному входу блока управления и к первому входу индикатора состояния сннхронизма, второй вход которого соединен с выходом второго триггера, а третий вход — с другим входом блока совпадения, с выходом дифференцнруюшего блока и через третий блок задержки — с другим входом второго триггера, причем вход дифференцирующего блока соеди нен с выходом тактового распределителя и с третьим дополнительным входом блока управления.

Индикатор состояния синхроннзма состоит из элемента И, выход которого соединен с индикатором через триггер, другой вход которого подключен к кнопке сброса.

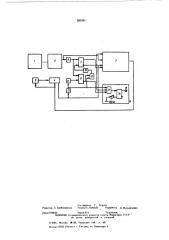

На чертеже дана структурная электрическая схема предлагаемого устройства.

Устройство цикловтэй синхронизации содержит последовательно соединенные формирователь 1 стробируюших имйульсов, ойознаварль

2 маркерного сигнала и блок 3 управления, выход которого соединен с входамн тактового

581591 распределителя 4 непосредственно и через делитель 5 частоты, а также индикатор.б состояния сннхроннзма, два триггера 7, 8, три блока

9, 10, ll задержки, блок 12 совпадения и дифференцирующнй блок 13. Выход опознавателя 2 маркерного сигнала подключен к входу первого блока задержки 9, выход которого соединен через первый триггер 7 с первым дополнительным входом блока 3 управления, а через последовательно соединенные второй триггер 8, блок 12 совпадения и второй блок 10 задержки — к другому входу первого триггера 7, выход которого подключен к второму дополнительному входу блока 3 управления и к первому входу индикатора 6 состояния синхронизма, второй вход которого соединен с выходом второго триггера 8, а третий вход — с другим входом блока

l2 совпадения, с выходом дифференцирующего блока 13 и через третий блок 11 задержки — с другим входом второго триггера 8, причем вход дифференцирующего блока 13 соединен с выходом тактового распределителя 4 и с третьим дополнительным входом блока 3 управления..

Индикатор 6 состояния синхронизма состоит из элемента И 14, выход которого соединен с индикатором 15 через триггер 16, другой вход которого подключен к кнопке 17 сброса.

Устройство работает следующим образом.

В исходном состоянии до поступления из канала связи первого синфазирующего импульса первый и второй триггеры 7, 8 установлены в

«О», триггер 16 — в

В конце первого такта с выхода дифференцирующего блока 13 пройдет импульс, опрашивающий блок 12 совпадения, и параллельно через блок ll задержки, устанавливающий второй триггер 8 в «О». Блок 12 совпадения в 1-м цикле заперт.

Во 2-м цикле работа устройства показана в установившемся режиме. Триггер 16 в установившемся режиме должен быть установлен в

«О» кнопкой 17 сброса от оператора. Первый триггер 7 постоянно находится в «1», синфазировка осуществляется через блок 3 управления, синфазировка осуществляется только в первом такте; если же через опознаватель 2 маркерного сигнала проходит импульс помехи вне первого такта, то ложной синфазировки нет. Второй триггер 8. ставится в «1» задним фронтом синфазирующего импульса через первый блок 9 задержки и ставится в «О» в начале второго такта через третий блок 11 "задержки.

В 3-м цикле работа устройства показана в случае искажения одного синфазирующего импульса: наложение помехи увеличило длительность импульса, в результате чего он не прошел через опознаватель 2 маркерного сигнала. В ре» зультате второй триггер 8 не установился в «1», и в конце первого такта через блок 12 совпадения прошел импульс, который через второй блок 10 задержки установил первый триггер 7 в

«О». Синфазировкн в этом цикле не произошло.

В случае искажения подряд второго синфазирующего им пульса (импул ьс отсутствует— замирание) в конце первого такта импульс с дифференцирующего блока 13 пройдет через элемент И 14 и установит триггер -16 в."«1».

Загорится световой индикатор 15, После вхождения системы в синхроннзм индикатор !5 будет гореть, пока оператор не зафиксирует его и не выключит кнопкой 17 сброса.

Предлагаемое устройство, по сравнению с известным, обладает повышенной помехоустойчивостью синфазировки.

Формула изобретения

1. Устройство цикловой синхронизации, содержащее последовательно соединенные фор25мирователь стробирующих импульсов, опознаватель маркерного сигнала и блок управления, выход которого соединен с входами тактового распределителя непосредственно н через делитель частоты, а также индикатор состояния синхронизма, отличающееся тем, что, с целью

ЗОповышения помехоустойчивости устройства, введены два триггера, три блока задержки, блок совпадения и дифференцирующий блок, при этом выход опознавателя маркерного сигнала подключен к входу первого блока задерж><кн, выход которого соединен чецез первый триггер с первым дополнительным входом блока управления, а через последовательно соединенные второй триггер, блок совпадения и второй блок задержки — к другому входу первого триггера, выход которого подключен к второму

® дополнительному входу блока управления и к первому входу индикатора состояния синхронизма, второй вход которого соединен с выходом второго триггера, а третий вход — с другим входом блока совладения, с выходом дифференцирующего блока и через третий блок задержки — с другим входом второго триггера, причем вход дифференцирующего блока соединен с выходом тактового распределителя и с третьим дополнительным входом блока управления.

2. Устройство по п. 1, отличающееся тем, что о индикатор состояния синхронизма состоит иэ элемента И, выход которого соединен с индикатором через триггер, другой вход которого подключен к кнопке сброса.

Источники информации, принятые во внима.ние прй экспертизе:

sS 1. Факторское свидетельство СССР ¹ 443491, М. Й 04 L Tg8, 1972.

58159 I

Составитель Г. Серова

Редактор Л. Гребенннкова Техред О. Луговая Корректор д Мельинценко

Заказ 4594/45 Тираж 815 Подписное

UHHH1IH Государственного комитета Совета Министров СССР но делам изобретений н открытий

113035, Москва, )К.35, Раушская наб., д. 4/5

Филиал ППП еПагентi. г. Ужгород. ул. Проектная, 4