Устройство временной коммутации асинхронных импульсных каналов

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (11) 581593 (6!) Дополнительное к авт. свид-ву(22) Заявлено 24,12,75 (21)2303264/18 0 с присоединением заявки № (23) Приоритет (43) Опубликовано 25.11.77. Бюллетень ¹43

:(4б) Дата опубликования описания Я2.12.1 1 (51) М, Кл.

Н 04 Lll/20

I/Н 03 К 17/00

Государственный комотет

Совета MNHNcTp05 СССР оо делам кзооретвннй я открытий (53) 7ДК 621.395, .345 (088.8) (72) Авторы изобретения

А, Ф, Леонов, В. В. Климов и С. П, Порхунов (71) Заявитель (54) УСТРОЙСТВО Н

АСИНХРОННЫХ

* 1 — ——

Изобретение относится к технике связи, Известно устройство временной коммутации асинхронных импульсных каналов, содержащее последовательно соединенные распределитель . временных каналов и блок памяти, первый выход которого через первый дешифратор подключен ко входам входных канальных комплектов,,первый и второй выходы которых подключены соответственно к первой информационной шине и шине передачи фазы, соединенной с входом анализатора фазы, первый выход которого подключен к первому входу переключающего блока, первый и второй выходы которого соединены соответственно с вторым и третьим входамн блока памяти, первый выход которого соединен с вторым входом переключающего блока, а выходы второго дешифратора подключены к первым входам выходных канальных комплектов, вторые входы которых соединены с второй информационной шиной 11).

Однако известное устройство не обладает достаточной пропускной способностью.

Цель изобретения — увеличение пропускной способности.

Для этого в устройство временной коммутации асинхронных импульсных каналов, содержаще последовательно соединенные распредеИМП УЛ ЬС НЫХ КАНАЛОВ

1 (2 ..,, о литель временных каналов и блок памяти, первый выход которого через первый дешифратор подключен ко входам входных, канальных комплектов, первый и второй выходы которых подключены соответственно к первой информаци-, онной шина и шине передачи фазы, соединенной со входом анализатора фазы, первый выход которого подключен к первому входу переключающего блока, первый и второй выходы которого соединены соответственно со вторым и

lo третьим входамн-блока памяти, первый выход которого соединен со вторым входом переключающего блока, а выходы второго дешифратора подключены к первым входам выходных канальных комплектов, вторые входы которых соединены со второй информационной шиной, 15 введены и последовательно соединенных элементов задержки и n+1 регистров, первые выходы которых соединены со второй информационной шиной, а вторые выходы регистров подключены ко входам второго дешифратора, при этом входы первого регистра соединены со входами первого элемента задержки, первый, второй и третий входы которого соединены соот. ветственно со вторым выходом анализатора фазы, первой информационной шиной и вторым выходом блока памяти, причем выходы элементов задержки подключены к входам соответст581593

Формула изобретения вующих регистров, а третий вход переключающего блока соединен с вторым выходом блока памяти.

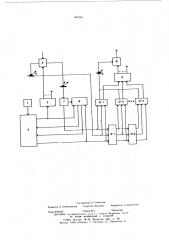

На чертеже дана структурная электрическая схема устройства временной коммутации асинхронных импульсных каналов.

I!редлагаемое устройство содержит последовательно соединенные распределитель временных каналов и блок 2 памяти, первчй выход которого ч рез первый дешифратор 3 подключен к входам входных канальных комплектов 4, первый и второй выходы которых подключены соответственно к первой информационной шине

5 и шине б передачи фазы, соединенной с входом анализатора 7 фазы. Первый выход анализатора 7 фазы подключен к первому входу переключающего блока 8, первый и второй выходы которого соединены соответственно с вторым и третьим входами блока 2 памяти, первый выход которого соединен с вторым входом переключающего блока 8. Выходы второго дешифратора 9 подключены к первым входам выходных канальных комплектов 10, вторые входы которых соединены с второй информационной шиной I I. В устройство введены п последовательно соединенных элементов задержки !

2-1 — 12-и и п+! регистров 13-1 — 13-(п+ !), первые выходы которых соединены с второй информационной шиной !1. Вторые выходы регистпов подключены к входам второго дешифр тора 9, при этом входы первого регистра 13-1 соединены с входами первого элемента задержки 12-1, первый, второй, третий входы которого соединены соответственно с вто рым выходом анализатора 7 фазы, первой информационной шиной 5 и вторым выходом бло<а 2 памяти, Выходы элементов задержки под<лючены к входам со ответствующих регистров.

Гретий вход переключающего блока 8 соединен с вторым выходом блока 2 памяти

>с гроиство временной коммутации асинхронных импульсных каналов работает следующим образом, Регистр 13-1-! 3- (и+ 1) выдают информационный импульс на вход второго дешифратора 9 и вторую информационную шину

11. На втором выходе анализатора 7 фазы при обработке очередного управляющего сигнала появляется кодовая комбинация К, соответствующая отклонению импульса проключения OT середины информационного импульса.

Кодовая комбинация с второго выхода анализатора фазы поступает на первый вход элем< нта задержки 12-1, ня eon второй вход поступает сигнал с первой информационной шины 5, а на третий вход — с второго выхода бло а 2 памяти.

В большинстве случаев величина К/Q 2 — 5 тактов. Количество элементов задержки должно быть равно 2К. В этом случае первый регистр 13-1 обеспечивает передачу информации на вход второго дешифратора У и вторук> информационную шину 11 при появлении на

55 шине 6 передачи фазы кодовой комбинации К, второй регистр -- К-1 и т.д. Каждое управлякнпее слово последовательно проходит по элементам задержки до тех пор.пока оно не будет считано одним из регистров. 11ри этом задержки или опережения импульсов проключения относительно характеристического момента восстановления, возникшие на предыдущих стугеиях коммутации, будут скорректированы.

1! редлага мое устройство может испол ьз 1ваться также при кодово-адресной коммутации.

В этом случае информацию о фазе могMo получать из канального комплекта или из промежуточных ступеней коммутации.

Технико-экономический эффект предлагаемого устройства заключается в уменьшении краевых искажений коммутируемых сигналов (увеличении пропускной способности группового тракта) и упрощении коммутации.

Устройство временной коммутации асинхронных импульсных каналов, содержащее последовательно соединенные распределитель временных каналов и блок памяти, первый выход которого через первый дешифратор подключен ко входам входных канальных комплектов, первый и второй выходы которых подключены соответственно к первой информационной шине и шине передачи фазы, соединенной с входом анализатора фазы, первый выход которого подключен к первому входу переключающего блока, первый и второй выходы которого соединены соответственно со вторым и третьим входами блока памяти, первый выход которого соединен со вторым входом переключающего блока, а выходы второго дешифратора подключены к первым входам выходных канальных комплектов, вторые входы которых соединены со второй информационной шиной, отличающееся тем, что, с целью увеличения пропускной способности, введены п последовательно соединенных элементов задержки и и+,1 регистров, первые выходы которых соединены со второй информационной шиной, а вторые выходы регистров подключены ко входам второго дешифратора, при этом входы первого регистра соединены со входами первого элемента задержки, первый, второй и третий входы которого соединены ссютветственно со вторым выходом анализатора фазы, первой информационной шиной и вторым выходом блока памяти, причем выходы элементов задержки подключены ко входам соответствующих регистров, а третий вход переключающего блока соединен с вторым выходом блока памяти.

Источники информации, принятые во внимание при экспертизе:

i. Авторское свидетельство СССР Ю 4346111, кл. Н 04 L I I/20, 1972.

Составитель Э. Гилинс кан

Редактор Л. Гребенникова Тепрел О. Луговая

Корректор A Кравченк<

Заказ 4594/45 Тираж 815 Г!однисное!

1!1!! Ill!I осударствсннспо комн « н с.овета Министров СССР по делам изобретений и открытий

l l 3035, Москва, Ж35, Раушская наб., n. 4/5

Филиал lll 111 «!1атент». г. Ужгород, ул. 11роектная, 4