Декодирующее устройство

Иллюстрации

Показать всеРеферат

О П И С А Н И Е 0)) 582564

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (61) Дополнительное к авт. свид-ву (22) Заявлено 15.07.76 (21) 2387093/18-09 с присоединением заявки № (23) Приоритет (43) Опубликовано 30.11.77. Бюллетень № 44 (45) Дата опубликования описания 07.12.77 (51) М. Кл.з H ОЗК 13/34

Н 041 1/10

Государственный комитет

Совета Министров СССР по делам изобретений и открытий (53) УДК 621.394.62 (088.8) (72) Авторы изобретения

В. И. Ключко, А. А. Ларин и С. П. Попов (71) Заявитель (54) ДЕКОДИРУЮЩЕЕ УСТРОИСТВО

Изобретение относится к вычислительной технике и может использоваться в устройствах защиты от ошибок систем передачи и обработки дискретной информации.

Известно декодиру|ощее устройство, содержащее три регистра сдвига, последовательно соединенные первый сумматор по модулю два, первый ключ, первый счетчик, решающий блок, второй ключ и второй сумматор по модулю два, а также перемножитель, третий ключ и блок обнаружения ошибки, выход которого соединен с другим входом решающего блока, при этом вход первого регистра сдвига и другой вход первого сумматора по модулю два объединены и являются входом устройства, а выход первого регистра сдвига соединен с первым сумматором по модулю два и блоком обнаружения ошибок (1).

Однако такое устройство конструктивно сложно из-за наличия большого количества регистров сдвига.

Цель изобретения — упрощение устройства путем исключения двух регистров сдвига и перемножителя.

Для этого в декодирующее устройство, содержащее последовательно сосдиненные регистр сдвига, первый сумматор по модулю два, первый ключ, первый счетчик, решающий блок, второй ключ и второй сумматор по модулю два, а также третий ключ и блок обнаружения ошибки, выход которого соединен с другим входом решающего блока, при этом вход регистра сдвига и другой вход первого сумматора по моду;по два объединены и яв5 ляются входом устройства, введен второй счетчик, причем другой выход решающего блока соединен с первыми входами третьего ключа и второго счетчика, вторые входы «оторых соединены с выходом первого ключа и

10 третьего ключа соответственно, а выход второго счетчика соединен с другим входом второго сумматора по модулю два, прп этом выход регистра сдвига также соединен с входом блока обнаружения ошибки и другим вхо15 дом второго ключа.

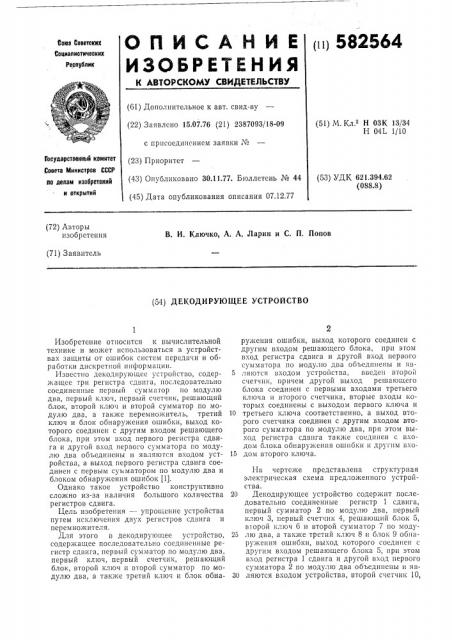

На чертеже представлена структурная электрическая схема предложенного устройства.

20 Декодирующее устройство содержит последовательно сосдиненные регистр 1 сдвига, первый сумматор 2 по модулю два, первый ключ 3, первый счетчик 4, решающий блок 5, второй ключ 6 и второй сумматор 7 по моду25 лю два, а также третий ключ 8 и блок 9 обнаружения ошибки, выход которого соединен с другим входом решающего блока 5, при этом вход регистра 1 сдвига и другой вход первого сумматора 2 по модулю два объединены и яв30 ляются входом устройства, второй счетчик 10, 582564

50 причем другой выход решающего блока 5 соединен с первыми входами третьего ключа 8 и второго счетчика 10, вторые входы которых соединены с выходом первого ключа 3 и третьего ключа 8 соответственно, а выход второго счетчика 10 соединен с другим входом второго сумматора 7 по модулю два, при этом выход регистра 1 сдвига также соединен с входом блока 9 обнаружения ошибки и другим входом второго ключа 6.

Устройство работает следующим образом.

Поступающая на вход устройства комбинация кода первого повторения записывается в регистр 1 сдвига. Во избежание преждевременного включения счетчиков 4 и 10, ключ 3 находится в закрытом состоянии и открывается по окончании записи комбинации первого повторения.

Комбинация второго повторения, осуществляя последовательный сдвиг предыдущей, подается на один из входов сумматора 2. Сдвигаемая из регистра 1 сдвига комбинация первого повторения одновременно поступает на другой вход сумматора 2 и в блок 9 обнаружения ошибок. Таким образом, одновременно с процедурой оценки достоверности, производимой блоком 9, происходит поэлементное сравнение обеих комбинаций. В случае необнаружения ошибки блоком 9 и идентичности двух повторений решающий блок 5, открывая ключ 6, обеспечивает вывод записанной в регистре сдвига комбинации на выход устройства.

В том случае, когда блок 9 не обнаруживает ошибки, а комбинация второго повторения оказывается искаженной, в результате поэлементного сравнения двух повторений на выходе сумматора 2 появляется импульс несовпадения в соответствующем разряде кодограммы, который включает счетчик 4 и с помощью ключа 8 запускает счетчик 10, который начинает счет поступающих на вход сумматора 2 разрядов комбинации.

Если в результате дальнейшего сравнения двух повторений не происходит несовпадения разрядов, на выходе счетчика 4 появляется сигнал «Одиночная ошибка». Решающий блок

5 на основании этого сигнала и отсутствия сигнала на своем первом входе обеспечивает коррекцкно искаженной комбинации тем, что он, осуществляя через второй ключ 6 вывод комбинации из регистра 1 сдвига на вход второго сумматора 7, не прекращает работы второго счетчика 10. Поскольку емкость счетчика 10 соответствует длине кодограммы, остаток его в момент окончания приема комбинации второго повторения соответствует местоположению искаженного разряда, поэтому импульс переполнения счетчика 10 поступает на вход сумматора 7 в тот момент, когда на другой вход последнего подается искаженный разряд комбинации второго повторения. Таким образом, осуществляется исправление одиночной ошибки.

Если блок 9 обнаруживает ошибку, а счетчик 4 фиксирует единственное несовпадение разрядов комбинаций двух повторений, то решающий блок 5 на основании сигналов

«Есть ошибка» на первом входе и «Одиночная ошибка» на другом осуществляет сброс счетчика 10 и ключа 8 в исходное состояние, обеспечивая вывод комбинации из регистра 1 сдвига на выход устройства.

Формула изобретения

Декодирующее устройство, содержащее последовательно соединенные регистр сдвига, первый сумматор по модулю два, первый ключ, первый счетчик, решающий блок, второй ключ и второй сумматор по модулю два, а также третий ключ и блок обнаружения ошибки, выход которого соединен с другим входом решающего блока, при этом вход регистра сдвига и другой вход первого сумматора по модулю два объединены и являются входом устройства, отличающееся тем, что, с целью упрощения устройства путем исключения двух регистров сдвига и перемножителя, введен второй счетчик, причем другой выход решающего блока соединен с первыми входами третьего ключа и второго счетчика, вторые входы которых соединены с выходом первого ключа и третьего ключа соответственно, а выход второго счетчика соединен с другим входом второго сумматора по модулю два, при этом выход регистра сдвига также соединен с входом блока обнаружения ошибки и другим входом второго ключа.

Источники информации, принятые во внимание при экспертизе

1. Бородин Л. Ф. Введение в теорию помехоустойчивого кодирования. М., Сов. радио, 1968, с. 189 — 191.

S82564

Составитель Е. Любимова

Техред E. Агафонова Корректоры: И. Позняковскаи и Л. Денискина

Редактор Т. Рыбалова

Подписное

Типография, пр. Сапунова, 2

Заказ 2594/12 Изд. № 962 Тираж 1080

НПО Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4(5