Устройство для сопряжения

Иллюстрации

Показать всеРеферат

И С А Н И Е „,5вз4 4

ИЗОБРЕТЕНИЯ

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт, саид-ву(22) Заявлено 25 03 76 (21)2339642/18-2 (51) М, Кл.

G 06 F 3/04 с присоединением заявки №Гасударственный комитет

Совета Министров СССР по делам изобретений и открытий (23) Приоритет

Ъ (43) Опубликовано 05,12.77, Бюллетень №4 (53) УДК 681Д27 (088.8) (45) Дата опубликования описания:26.12.77 (72) Автор изобретения

В. В. Иванов

Ордена Ленина институт кибернетики AH Украинской ССР (71) Заявитель (54) УСТРОЙСТВО ДЛЯ СОПРИКЕНИ Я

Изобретение относится к вычислительной технике и может найти применение в многомашинных системах для сопряжения между

3BN и с аппаратурой передачи данных.

Известны устройства сопряжения, содер- 5 жашие оперативные запоминаюшие устройся ва на сдвигаюших регистрах, группы венти лей по числу регистров, реверсивный тактовый распределитель формирователь импульсов сдвига, вход и выход синхронизации 1 1 ), Однако эти устройства, обладают низкой надежностью, так как возможно искажение информации, если скорость ввода в память устройства превышает скорость вывода из памяти.

Наиболее близким к изобретению по технической сути является устройство сопряжения, содержашее распределитель и блок паметию включаюший-еруппу сдвиговых регистров и матрицу элементов И по одному ие каждыйхо разряд регистра Выходы элементов И матрицы соединены 1с информацйонным входом

=оответствуюшего-разряда сдвигового регистра, выходы .первых разрядов каждого сдвигового регистра подключены к соответствую- 5

2 шему информационному выходу устройства, первые входы элементов И каждой строки матрицы соединены с соответствуюшим информационным входом устройства, вторые входы элементов И каждого, столбца соединены с соответствуюшим выходом распределителя, первый вход которого подключен к первому входу синхронизации ввода устройства 121 .

Недостатками этого устройства является его сложность и невысокая надежность.

Мелью изобретения является упрошение. устройства,,@ля 1этого устройство содержит элемент

И, элемент ИЛИ-HF, и формирователь импульсов сдвига, причем три входа элемента ИЛИНЕ соединены соответственно с первым, вторым и третьим входами синхронизации ввода устройства, а выход - с первым входом элемента И, второй вход которого подключен к входу синхронизации вывода устройства, второй вход распределителя,.и входы продвиже-. ния сдвиговых регистров соединены с выходом формирователя импульсов сдвига, вход которого подключен к выходу элемента И.

583424

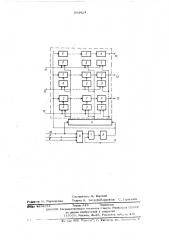

На чертеже представлена структурная схема устройства, Устройство содержит блок 1 памяти, вялючающий сдвиговые регистры 2 и элементы

И 3 матрицы, распределитель 4, формирователь 5 импульсов сдвига, элемент ИЛИ-HE

6, элемент И 7, входы 8, 9 и 10 синхронизации ввода, вход 1 1 синхронизации вывода, информационные входы 12 и информационные выходы 13. to

Устройство работает следующим образом, Код, поступающий иэ источника на входы

12 для записи в блок 1, сопровождается се-. рией импульсов по входам 8, 9, 10. Первый импульс этой серии, появляющийся на входе i5

8, осуществляет блокировку поступления сигналов синхронизации вывода на входе 11 и разрешает завершение операции вывода кода, если эта операция (началасьвпредшествующий моментвремени. При наличии сигнала на вх Ю де 8 код на входы 12 не подается. По. окончании сигнала на входе 8 появляется сигнал н" входе 9 и код на входах 12. В интервале присутствия сигнала íà axon 9 происходит запись в соответствующие разряды сдви- 25 говых регистров 2 кода, присутствующего на входах 12. По окончании записи и пропадании сигнала на входе 9 появляется сигнал на входе 10, который сдвигает распределитель 4 на один шаг влево подготавливая к записи зо очередного кода в соответствующие разряды сдвиговых регистров 2.

После снятия импульсов с входа 10 элемент И 7 разблокируется, и может ocymecTвляться вывод кодов иэ бл ока 1 памяти, При 35 этом каждый импульс на входе 11 пр двигает распределитель 4 и информацию в сдвиговых регистрах на один щаг вправо, так что распределитель 4 фактически всегда находи вся на ячейка блок@ 1, куда можно записывать40 очередной «од, Таким образом. устройство обеспечивает продтрфввод и Вывод информации и при этом гарантирует невозможность наложени.т информации, Ф ормула изобрете ни я

Устройство для сопряжения, содержащее распределитель и блок памяти, включающий группу сдвиговых регистров и матрицу элементов И по одному Н8 каждыйразрядкажцого регистра, выходы элементов И матрицы соединены с . информационным входом соот ветствующего разряде сдвигового регистра, выходы первых разрядов каждого сдвигового регистра подключены к соответствующему информационному выходу устройства, первые входы элементов И каждой строки матрицы соединены с соответствующими информационным входом устройства, вторые входы элементов

И каждого столбца соединены с соответству ющим выходом распределителя, первый вход которого подключен к первому входу синхро низации ввода устройства, о т л и ч а ю—

ut е е с я тем, что, с целью упрощения устройства,. оно содержит элемент И, элемент

ИЛИ»НЕ и формирователь импульсов сдвига, причем три входа элемента ИЛИ-НЕ соединены соответственно с первым,, вторым и третьим входами синхронизации ввода устройства, а выход — с первым входом элемента И, второй вход которого подключен к входу синхронизации вывода устройства, второй вход распределителя и входы продвижения сдвиговых регистров соединены с выходом формирователя импульсов сдвига, вход которого подключен к выходу элемента И.

Источники- информации, принятые во внимание при экспертизе:

1. Авторское свидетельство СССР

34 401999, М, кл, G 06 F 13/02, 1971., 2; Заявка No . 2166167/24, М. кл. G06 F 3/Î4, 1 975, по которой принято решение о выдаче авторского свидетельства.