Микропрограммное устройство управления

Иллюстрации

Показать всеРеферат

ОЙ ЙСАНИЕ

ЙЗОБРЕТЕН ИЯ

К AST РЮМОЧКУ СВИДИИЙЬСТВУ (11) 583434 (61) Дополнит льное к авт. свид-ву (5 .} М. Кл.

806 V 9/.12 (22) Заявлено 22,12 75 (21) 2302256/

/18-24. с присоединением заявки №

Государственный номнтет

Совета Министров СССР ла делам изобретений и втнрытнй (23) Приоритет(43) Опубликовано 05,12,77. Бюллетень №4 (53) УДК681.325 (088.8 ) (45) Дата опубликования описания 20.12.77

В, Х, Балаев, В. И. Евдокимов и А. И, Самоваров (72) Авторы изобретения (71) Заявитель (54) МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВГ1ЕНИЯ

Изобретение относится к вычислительной технике и может быть использовано в упраряющих устройствах систем коммутации сообщений.

Известно устройство для управления об- 5 работкой программ, имеющих различный приоритет, в установке для обработки данных (11.

Недостатком этого устройства является 10 необходимость затрат времени на выполнение арифметических операций для определения программы, имеющей в данный момент наивысший приоритет, 15

Наиболее близким к иэобретению техническим решением является устройство программного управления для системы дальней телефонной связи управляем ой сосредоточенноо хранимой программой,содержащее входные регистры, дешифраторы, микропрограммную память, адресные элементы И, элемент ИЛИ, генератор тактовой частоты, развертывающий блок и элемент И запуска развертывающего блока t 21, Недостатком устройства является значительные временныо затраты на выбор мик ропрограмм, так как выбор микропрограммы, имеющей наивысший приоритет по сравнению с остальными микропрограмма;ли, находяши4 мися в очереди, осуществляется последовательным просмотром приоритетов и анализом очередей заявок всех микропрограмм.

Белью изобретения является сокращение времени выборки программ, Для этого устройство содержит делители частоты, входы которых соединены с выходом генератора тактовой частоты, а выходыс первыми входами адресных элементов И, . к вторым входам. которых подключены выходы дешифраторов, входами оэединенных с выходами входных регистров, управляющие входы которых подключены к выходам соответствующих адресных элементов И, к соот1зетствуюшим адресным входам микропрограммной памяти и к соответствующим входам элемента ИЛИ, выход которого подключен к первому входу элемента И запуска развертывающего блока, второй вход которого соединен с выходом генератора тактовой

583434

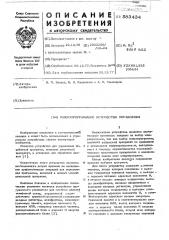

Адресные элементы И. 3 предназначены ала непосредственной выборки подпрограммы, имеющей наибольший приоритет в данный момент, для включения в работу.

Микропрограммная память 9 предназначена для хранения выполняемых в управляющем устройстве подпрограмм. Она представ» ляет собой одностороннее запоминающее устройство, состоящее из эон, каждая иэ которых хранит одну иа К выполняемых в устройстве программ.

Делители частоты представляют собой набор автономных делителей частоты, которые могут быть выполнены любым из способов, известных в импульсной технике. На вход каждого из делителей поступает сигнал основной частоты с выхода генератора тактовой частоты. С выхода каждого иэ де. лителей частоты на входы адресных элементов. И 3 выдаются потенциальные .сигналы,.причем выдача каждого иэ этих сит налов осуществляется с заранее установлен. .ной частотой включения соответствующей программы, 55

Развертывающий блок 8 осуществляет развертку последовательностей команд, со ставляющих подпрограммы, во времени, Устройство работает следующим образом.

60 35 частоты," выход элемента H запуска .развер тывающего блока соединен со входом раз вертывакяпего блока, выходы которого под включены к соответствующим управляющим входам микропрограммной памяти."

На чертеже представлена структурная схема предложенного устройства, Устройство содержит входные регистрьз, 1, дешифраторы 2, адресные элементы И 3, генератор тактовой частоты 4, делители 5 частоты, элемент И 6 запуска развертывающего блока, элемент ИЛИ 7, развертывающий блок 8 и микрэпрограм иую память 9.

Регистры 1 предназначены для записи и хранения кодов номеров подпрограмм, заявки 5 на выполнение которых поступают в управляющее устройство узла коммутации. Номер регистра сг ответствует номеру подпрограммы. Каждый иэ регистров состоит иэ нес- ° кольких последовательных групп разрядов, Число разрядов в группе определяется разрядностью кода номера подпрограммы,. Каждая группа рассчитана на запись и хранение кода номера одной подпрограммы„

Дешифраторы 2 представляют собой обычные матричные дешифраторы для преоб разования параллельных кодов, поступающих с выходов регистров 1 в потенциальные сигналы, которые далее подаются на элементы И, 30

Переход к выполнению очередной подпрограммч после окончания выполнения любой предыдущей жестко предопределен заложенной s схеме устройства организацией включения подпрограмм в соответствии с заранее заданными частотами обращения, включения) к подпрограмме в течение цикла рабрты процессора. Количественное значение частоты обращения к данной подпрограмме определяет ее приоритет.

Во входных регистрах 1 записываются коды номеров подпрограмм, заявки на выполнение которых поступают в управляющее устройство, причем код номера первой подпрограммы записывается в первый регистр 1, код номера второй подпрограммы во второй. регистр 1 и т.д. Поступающие коды записываются в каждом иэ регистров последовательно, один за другим. Из регистров 1 коды поступают на соответствующие дешифраторы 2, Коды номеров подпрограмм преобразую ся в закрепленных за этими подпрограммами дешифраторах 2 в потенцииьные сигналы, поступающие на входы соответствующих адресных элементов И 3. На другие входы адресных элементов И 3 подаются сигналы включения с частотами, различными для каждой из подпрограмм. В результате появ ляется сигнал на выходе только того адрес ного ел мента ИЗ, который соответствует подпр ограмме, на к оторую, в о-первых, имеется запрос на включение, и, во вторых, для которой наступил момент обращения к ней, определяемый сигналом включения, выдаваемым соответствующим этой подпрограмме делителем частоты, Сигналы с выходов адресных элементов

И 3 поступают также н элемент ИЛИ 7 и далее на элемент И 6. На второй вхоч эле мента И 6 поступает тактовый импульс от генератора тактовой частоты 4. Импульс с выхода элемента И 6 запускает развертывающий блок 8.

Сигнал с выхода одного из адресных элементов И 3, соответствующий выбранной подпрограмме, поступает на соответствующую этой подпрограмме секцию микропрограммной памятии 9, в результате чего начинают считываться (при одновременном поступлении сигналов с выхода развертывающего блока 8) микрокод анды, составляющие данную подпрограмму. После выдачи одним из адресных элементов И 3 сиг нала включения одной иэ подпрограмм при помощи этого же сигнала осуществляется сдвиг к дов в соотвежт ующем входном регистре 1.

583434

Для работы предлагаемого устройства не требуются специальная программа, изме-: няющая состояние регистра зашиты, и осуществеление процедуры последовательного просмотра и анализа очередей заявок на выполнение всех подпрограмм, Исключением процедур просмотра и анализа достигаетса сокращение затрат времени на процесс вьг-, бора подпрограмм, Формула изобретенйя ю

Микропрограммное устройство управления, содержащее входные регистры, дешифраторы, микропрограммную память, адресные элементы И, элемент ИЛИ, генератор тактовой частоты, развертывающий блок и элемент И 15 запуска развертывающего блока, о т л ич а ю ш е е с я тем, что, с целью сокращения времени выборки программ, оно включает делители частоты, входы которых соединены с выходом генератора тактовой ча- 20 стоты, а выходы - с первыми входами адресных элементов И, ко вторым входам ко6 торых подключены выходы соответствующих дешифраторов, входами соединенных с выходами входных регистров, управляющие входы которых подключены к выходам соответствующих адресных элементов И, к супер" ! ветствуюшим адресным входам микропрс граммной памяти и к соответствующим входам элемента ИЛИ,выход которого подключен к первому входу элемента И запуска развертывающего блока, второй вход которого соединен с выходом генератора тактовой частоты, выход элемента И запуска развертывающего блока соединен со входом развертывающего блока, выходы которого подключены к соответствующим управляющим входам микропрограммной памяти.

Источники информации принятые Во вни мание при экспертизе:

1. Пате д ФРГ No 20294 67, кл.

6 06 F 9/18, 17.02.1972.

2. Патент США М 3636522, кл.

340-172.5, 18.01.1972.

Составитель В, Евстигнеев

P И Марховская Техред Н. Бабурка, Корректор В. Сердюк

Редактор

Заказ 4895/54 Тираж 818 Подписное вета Минист ов СССР

UHHHHH Государственного комитета Совета Мин с р по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. /, 4/5

Филиал ППП "Патент", r. Ужгород, ул, Проектная, 4