Устройство микропрограммного управления

Иллюстрации

Показать всеРеферат

Союз Совет@них

Социалистических

Республик (1: 583435 (о1) Дополнительное к авт. свид-ву(22) Заявлено 11,02,76 (211 2З 24477/ 18-24 с пр!!соединением заявки №

{51) М. Кл, 606 F 9/16

1аеударатвенный намитет

Совета Министров СССР

° no делам изобретений и еткрь тий (23) Приоритет(43) Опубликовано 05,12.77. Бюллетень %45 (53) УДК 681,325 (088,8) (45) Дата опубликования описания 2.0,12. 77 (72) Автор изобретения

В, А. Платонов

Таганрогский редиотехнический институт им, В, Q. Калмыкова (71) Заявитель (54 ) УСТРОЙСТВО МИКРОПРОГРАММНОГО УПРАВЛЕН ИЯ

Изобретение относится к вычислительной технике, в частности к устройствам микропрограммного управления, и может быть использовано при создании микропрограммных процессоров.

Известно устройство микропрограммного управления, содержащее блок композиционной памяти, усилители, дешифратор, схему выбора, регистр ы а прес а м икр окоман ды, схему управления, группы схем И, группу 10 схем ИЛИ, триггер управления, блок объединения признаков условного перехода, элементы И, ИЛИ 11.

Однако для его реализации необходимы значительные затраты оборудования, 15

Наиболее близким к изобретению по технической сущности и достигаемому резулн тату является устройство микропрограммна го управления, содержащее блок постоянной памяти, выход которого соединен с ре гистром микрокоманды, дешифратор микрокоопераций> выход которого соединен с первым входом формирователя функциональных сигналов, регистр кода операции, выход которого с ое динен с первым входом регистра

2 адреса, блок синхронизации, выход карого соединен со вторыми входами формирователя функциональных сигналов и регистра, адреса,с первым входом блока постоянной памяти, причем первый, второй выходы регистра микрокоманды соединены соответственно со входом деШифратора микроопераций и с третьим входом регистра адреса, выход которого соединен со вторым входом блока постоянной памяти, а выход формирователя функциональных сигналов. является первым выходом устройства (2j

Однако процесс составления машинных программ, например, для вычисления сложных математических выражений осуществляется либо вручную, либо с помощью специальной обрабатывающей программытранспятора, что увеличивает общее время решения задачи, т.е. снижает быстродейсч вие устройства.

Цель изобретения — повышеыие быстро действия устройства. ,Бля этого устройство содержит первый и второй блоки магазинной памяти и блок сравнения приоритетов символов, причем выход формирователя функциональных сйгнадов соединен с первыми входами второго блока магазинной ламяти и блоке сравнения приоритетов символоВ, Второй Вход и первый, щорой выходы которого соединены соот о г ветственно с выходом и входом первого блока магазинной памяти и со входом ре. гистра кода операций, третий вход блока сравнения приоритетов символов, второй вход и вы:од второго блока магазинной

10 памяти являются соответственно первым, вторым входами и вторым выходом усТ ройства.

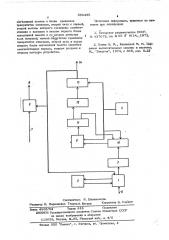

На чертеже приведена структурная схема

i 15 устройства.

Устройство микропрограммного управления содержит блок 1 сравнения приори»

20 кетов опмвопов, первый блок 2 мвгевиквой памяти, регистр 3 кода операции, блок 4 синхронизации, второй блок 5 магазинной памяти, входы 6,7, выход 8, блок 9 постоянной памяти, регистр 10 адреса, ре гистр 11 микрокоманды, дешифратор,12 микроопераций, формирователь 13 функциональных сигналов, выход 14, Устройство работает следующим образом, нается анализ следующего символа, посту» пившего ко входу 6.

Функциональный символ, записанный в регистр 3, передается в регистр 10, где определяется фиксированный адрес ячейки блока 9, начиная с которой записана микропрограмма выполнения операции, опреде ляемой кодом операции в регистре 3.

Из блока 9 последовательно выбираются ! микрокоманды, дешифрируются дешифрато- ром 12, и по ним формирователем 13 формируются функциональные сигналы, которые используются для выборки из блока 8 оче редных операндов. Эти же сигналы исполь.— зуются для управления работой арифметикологического.блока и других блоков процессора (на чертеже не показаны) по выполненик1 операций над выбранными операндами.

Результаты выполнения операции записываются в блок 5, а в блок 1 подается управляющий сигнал, разрешающий запись следующего символа в регистр 3. Так продолжается до тех пор, пока не будет решена вся задача, Изобретение позволяет увеличить быстродействие устройства путем устранения необходимости использования специальной программы, а также за счет совмещения этапа трансляции с этапом решения.

Операции, имеющие больший приоритет, выполняются раньше . тех, которые имеют меньший приоритет. Поэтому, если поступивший фУнкциональный GHMBQH HMeBT HB 55 больший приорит т, не больший находящего» с." на выходе бчоке 2, то функциональный символ извлекается иэ блока 2 и записывается в регистр 3. Если же наоборот, то поступивший символ записывается в блок 2 > в качестве очередно о, а s блоке 1 начи

Решаемая задача, например система дифференциальных уравнений в нормальной форме, записанная вместе с начальными значениями функций и производных на алгоритмическом языке, поступает в порядке записи на входы 6,7 устройства. Причем, функциональные символы и разделители по и ступают по входу 6 в блок 1, а операнды (числа и символы переменных) по входу 7 в блок 5 и заполняют его в порядке постуи ления таким образом, что на выходе блока, 5 всегда находится операнд, записанный в тот блок последним, /

В блоке 1 происходит сравнение приоритета символе, поступившего по входу 6 с приоритетом символа, находящегося на вы ходе блока 2.

Формула иэобрете ния

Устройство микропрограммного управле-: ния, содержащее блок постоянной памяти,— выход которого соединен с регистром микрокоманды, дешифратор микрокоопераций, выход которого соединен с первым входом формирователя функциональных сигналов, регистр кода операции, выход которого соединен с первым входом регисчра a реса, блок синхронизации, выход которого соединен со вторыми входами формирователя функциональных сигнелов и регистра адре са, с первым входом блока постоянной па- . мяти, причем первый, второй выходы регистра микрохоманды соединены соответственно со входом дешифратора микроопераций и с третьим входом регистра адреса, выход которого соединен со вторым входом блока постоянной памяти, а выход фор- мирователя функциональных сигналов являеъся первым выходом устройства, о т л ич а ю щ е е с я тем, что, с целью повышения быстродействия, оно содержит первый и второй блоки магазинной памяти и блок сравнения приоритетов символов, причем выход Формирователя функ иональных сигналов соединен с первыми входами второго блока

583435 5 магазинной памяти и блока сравнения приоритетов символов, второй вход и первый, второй выходы которого соединены соотЬет.ственно с выходом и входом первого блока магазинной памяти и со входом регистра

: кода- операций, третий вход блока сравнения приоритетов символов, второй вход и выход второго блока магазинной памяти являются соответственно первым, вторым входами и вторым выходом устройства, Источники информации, принятые во внимание при,зкспертйзе:

1, Авторское свидетельство СССР, N. 437073, кл. G 06 Р 9/14, i 1972, 2. Каган Б. М,, Каневский М. N. цифровые вычислительные машины и системы, М., "Энергия, 1974, с 365, рис. 5-27

Составитель P. Шашахметов

Редактор И. Марховская ТехредА, богдан Корректор В. Серйок

Заказ 4895/54 Тираж 818 По дписное

БНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4