Буферное запоминающее устройство

Иллюстрации

Показать всеРеферат

Союз Советскин

Социадистимескик

Республик (11i 583476 (61) дополнительное к авт. свил-ву (22) Заявлено 13.01.76 . (21)2315157/18-2 с присоединением заявки № (23) Приоритет (51) М. К..Р

G 11 С 11/00

Гооударотввнный квинтет

Совета тйнннотроа СССР но,аеяам наабретеннй н открмтнй (43) Опубликовано 05.12.77. Бюллетень №45 (53) УДК 681.327, .66 (088.8) (45) Дата опубликования описания 20 12-77 (72) Авторы изобретения

В. С. Голубев и Ю. В. Сулимов (7!) Заявитель (54) БУФЕРНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

Изобретение относится к области вычиспитепьной техники.

Известйо буферное запоминаюшее устройство (БЗУ), которое позволяет передавать информацию в одном направлении. Недостат- 5 ком данного устройства является невозможность передачи информации в двух направпениях (Ц.

Наиболее бпиэким к изобретению являет- . ся БЗУ (2), содержашее накопитепь, один !О из входов которого соединен через первую группу элементов И с входными шинами и управлявшими шинами записи, а выход через вторую группу эпементов И соединен с выходными шинами и управпяюшими шинами 15 считывания, блок формирования адресов записи и считывания, выходы которых подкпючены ко входам схемы сравнения. Выход схемы сравнения соединен с одним иэ входов первого эпемента И, другой вход кото- 20 рого подкпючен ко входу бпока формирования адресов считывания и первой адресной шине. Выход первого элемента И соединен с одним иэ входов первого элемента ИЛИ, другой вход которого соединен со второй 25 адресной шиной, а выход - со входом бпока формирования адресов записи, Недостатком такого устройства являются ограниченные функциональные возможности, например, в старт-стопных системах передачи (приема) информации необходимо испопьзовать два накопителя со схемами управления: один - дня согласования канала передачи информации, другой - дпя согласования канала приема информации.

Кепью изобретения является расширение области применения устройства.

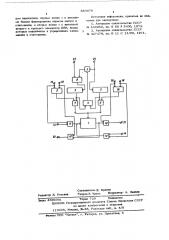

Дпя достижения поставленной цели предпоженное устройство содержит второй и третий элементы И и ИЛИ. Выходы второго и третьего элементов И соединены с другим входом накопителя, первые входы - с выходами блоков формирования адресов записи и с итывания, а вторые входы - с выходами второго и третьего эпементов ИЛИ, входы которых подключены к управпякщим шинам записи и считывания, На чертеже представлена структурная схема предлагаемого устройства, 5834-6

Устройство содержит накопитель 1,, блок формирования адресов записи 2, блок формирования адресов считывания 3, схему сравнения 4, первый элемент И 5, первый элемент ИЛИ 6, второй 7 и третий 8 элементы И, второй 9 и третий 10 элементы

ИЛИ, первую группу элементов И 11, 12, выходы которых подключены к одному из входов накопителя, а входы — к входным шинам 13, 14 и управляющим шинам запи- о си 15, 16, вторую группу элементов И 17, 1 8» ВХОДЫ KGTopblx подключены K ВыхОду накопителя и к управляющим шинам считывания 19, 20, а выходы - к выходным шинам 21, 22, 35

Сигналы смены адреса в блоках 2 и 3 поступают сО ВтОрОй 23 и первой 24 аДресHbI X ШИН.

Устройство работает следующим образом, Ввод информации, поступающей на Входные шины 13, 14, в накопитель 1 осуществляется через первую группу элементов И

11, 12.

ВывОд информации из накОпителЯ 1 Ocg ществляется через вторую группу элементов >>

И 17, 18.

ВВОД (Вывод) инфОрмации В (нз) накопи тель осуществляется по адресам, которые формируются в блоках 2 и 3, и поступают в накопитель через элементы И 7 и 8, на вто=рые входы которых подаются управляющие сигналы элементов ИЛИ. 9 и 10. Схема сравнения 4 элемент И 5 и элемент ИЛИ 6 обеспечивают сравнение адресов в блоках

2 и 3 н их установк в пОлОжении, при ко» з3 тором адрес записи блока 2 никогда не Отстает от адреса считывания блока 3, Подгон адреса записи Осугцестаг»яется сигна лом смены адреса, формирукнпнмся на rep

ВОй адреснОй шине 24 и поступахОщнм через элемент И 5 и элемент ИЛИ 6 На Вход блока 2.

Последовательность ввода и вывода информации из накопителя 1 определяется уп-, раВляющимн сигналами HG шинах 1 5, 16, 19 и 20, которые формируются в завис и

МОСТИ OT СОСТОЯНИЯ ЛИНИИ СВЯЗИ, В режиме Линия связи свободна иггфор-. мация мОжет п»Оступать по каналу передачи у и по каналу приема. При этом на шину 20 с поступает сигнал, обеспечивающий считыва нне передаваемой В канал связи инфОрмацни по адресу, формируемому блоком 3, и ее вывод производится В канал связи IIQ гпнне уу

2 1, HG шину 1 6 поступает сигнал, GoecIIB чивающий запись приннмаемОй HG канала и»формации по адресу, который был опрошен и а освобожден по сигналу, постуг»ившему такте»»»а ггину 63

19 поступает сигнал, обеспечивающий счжты Ванне принятой из линни связи информа ции н ее вывод на выходные шины 22, на шину 15 поступает сигнал, обеспечивающий запись информации в накопитель по адресу, поступившему с шины 19 в предыдущем такте, Сигналы смены адреса ПОступ&ют на шины 23 н 24 поочередно, при этом частота поступления сигналов на шину 23 определяется частотой работы приемного и передающего аппаратов, а частота поступления сигналов на шину 24 — скоростью переда чи информации в линию связи.

В режиме Линия связи занята передача информации в линию связи и прием ее из линии связи отсутствует. При этом управлякг шие сигналы на шины 20 н 16 и сигналы смены адреса на шину 24 не поступают. В данном режиме подаются управлягощие сигнальг на шины - 19 и 15, а сигналы смены адреса — на шину 23. При этом осуществляет-,я вывод принятой информация и запись

В накопитель информации, постутгающей по

Бходггым шинам, Прн заполнении накОпителЯ запись ггрееращается.

ГгпедлU BHHQB БЗУ 4ожет 6bITb использоВаноэ HagpHMåp» B старт-стопных синхронных система передачи j пpиема) нггформащщ и слу-гаях, KGF Aa информаг»ия передается в двух направлениях с промежуточным хранением в памяти. При этом coKpalHGBTOH количество оборудования за счет более эффективного исгггользованггя Одного накопителя Вместо двух»

Уменьгггаютси потг.еблЯемая мощнОсть GIIIIGPG

-G и затраты на его изготовление.

ВуФерное загтог,гинагощее ус тройсво с р

ABpKaøBB накопитель» QAHH из В одов кото

РО1 О CeieigHHBH»IBPBG HBPB»JIO ГРУггПУ ЭЛЕМЕН=» тов И с Входными шгвами H управггяющнмн шинами записи» выход чепез Вторую группу элсментОВ И-с ВыхОдными шинами H упраиля»ощими шинами считыВания блОки форми рования адресов BGIIHQH и считывания, выхО ды .КОторых подклгочены кО вхОдам схемы сраВнения ВьгхОдом соединенной с Одним из входов первого элемента И, другой вход которого подключен ко входу блока формирования адресов счнт&ваг»ня и ггервой адресной шине, выход первого элеменTG И соедннен с одним из входов первого элемента И г гИ» другои Вхбд котОрогО cQBAR нен со Второй адресной шиной, а выход со ВхОдом блОка ФОрмнровання адресов GG циси,ОтличающeеcяTBMчтО, с пелью расширения области применения

УстРойства, GRQ содеРжит BTQPGN H TPBT LN элементы И и ИЛИ; выходы второго и третьего элемента И соединены с другим Вхо

583476

Составитель: В. Фралов

peääóó ô д, текина Техред Э Чужие корректор"

3аказ 4899/56 Тираж 729 Подписное

БНИИПИ Государственного комитета Совета Министров СССР до делам изобретении и открытий

1 1 3035 ц осква, Я(-35 Р с: я ++6 4/g

Филиал ППП Патент, г. Ужгород, yri, Проектная„4 дом накопителя, первые входы - с выходами блоков формирования адресов записи и считывания, а вторые входы — с выходами второго и третьего элементов ИЛИ, входы которых подключены к упраалякхпим шинам записи и считывания.

Источники информапия, принятые во вни мание прн экспертизе:

1. Авторское свидетельство СССР

¹ 446052, кл. G 06 f 5/00, 1973.

2. Авторское свидетельство, СССР

¹ 427379, an. О 11 С 11/00, 1971.