Буферное запоминающее устройство

Иллюстрации

Показать всеРеферат

Союэ Советских

Социалистических

Республик (»i 583478 (6l) Дополнительное к авт. саид-ву (22) Заявлено 06.02.76 (21)2321639/18-2 с присоединением заявки №(23) Приоритет(43) Опубликовано 05.12.77. Бюллетень №4 (45) Дата опубликования описании 20.12.77 (ю 11 С 11/00

Государственный комитет

Совета Министров СССР но делаю нэоорвтеннй

N DTICPblTNN (53) УДК 681.327..6 (088.8) (72) Авторы изобретения

М. В. Мусин и Т. И. Баранова (71) Заявитель (54). БУФЕРНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

Изобретение относится к области запоминающих устройс гв.

Известно буферное запоминающее устройство; (БЗУ) содержащее счетчик, элементы

И, элементы задержки, элемент памяти и блок управления f 1).

Недостатком этого устройства является

Ю то, что при большой неравномерности постуйления входной информации происходит иере полнение счетчика, что снижает надежность работы устройства.

Наиболее близким техническим решением к изобретению является БЗУ, содержащее счетчики импульсов считывания и записи, первые выходы которых подключены через дешифраторы считывания и записи ко входам накопителя, вторые выходы соединены со входами компаратора, элемент задержки, подключенный через первый элемент И ко входу счетчика импульсов считывания, третьи выходы которого соединены со вторым элементом И, третий, четвертый и пятый элементы И, триггеры и тактовые шины записи и считывания (2).

Недостатком этого устройства является сложность и ненадежная работа при больших неравномерностях поступления входной информации. Например, при аварийных режимах переполнения происходит не только потеря информации, но и наложение ее на ранее записанную информацию в накопителей.

Цель изобретения - упрощение и повыше» ние надежности устройства при аварийных режимах переполнения.

Поставленная цель достигается тем, что в предложенном устройстве выход второго элемента И цод.ключен к нулевым входам первого и второго триггеров. Третьи выходы счетчика импульсов записи через третий элемент И подключены K единичному входу второго триггера, прямой выход которого через четвертый элемент И соединен с единичным входом первого триггера. Входы пятого элемента И. подключены соответственно к выходам компаратора, к тактовой шине считывания н инверсному выходу второго триггера, а выход пятого элемента И соедв нен с нулевым входом третьего триггера.

Инверсный выход первого триггера и прямой

583478 выход третьего триггера соединены соответственно с блокирующими входами дешифраторов записи и считывания. Тактовая шина записи подключена ко входам счетчика импульсов записи и четвертого элемента И и к единичному входу третьего триггера.

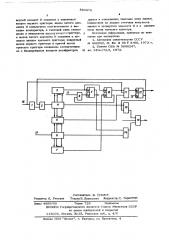

На чертеже изображена структурная схема предложенного устройства.

Устройство содержит элемент задержки

1, первый 2 и вгорой 3 элементы-й, счет- 1î чик импульсов. считывания 4, компаратор 5, счетчик импульсов записи 6, третий 7 и

„ четвертый 8ележентыИ, первый 9 и второй

10 триггеры,-пятый элемент И 11, третий триггер 12, дешифраторы считывания 13 и записи 14, накопитель 15, такговые шины считывания 16 и записи 17.

Первые и вторые выходы счетчика 6 соединены соответственно со входами дешифратора 14 и компаратора 5.

Выход элемента И 3 подключен к нулевым входам триггеров 9 и 10. Третьи выходы счетчика 6 через элемент И 7 подключены к единичному входу триггера 10, пря25 мой выход которого через элемент И 8 соединен с единичным входом триггера g. Bxo

Ф ды элемента И 11 подключены соответствен но E выходам камн&ратора 5y х тактовой шине считывания 16 й--инверсному выходу

30 триггера:,10, а выход элемента И 11 соеди нен с нуриевым входом триггера 12. Инверсный выхол триггера 9 и прямой выход триггера 11 соединены соответственно с блокирующими входами дешифраторов записи 14 и считывания 13. Тактовая шина записи 17 подключена ко входам счетчика импульсов записи 6 и элемента И 8 и, единичноМу входу триггера 12, Устройство работает следующим образом.

В исходном состоянии счетчик И и .тритъ .геры находятся в нулевом положении, поэтому такт считывания, пришедший .раньше такта записи, на счетчик 4 не проходит. Это происходит потому, что на единичном выходе триггера 12 присутствует низкий потенциал, поступающий на вход элемента И 2.

При поступлении такта записи триггер

12 меняет свое состояние, и дешифратор

13 и элемент И 2 разблокируются.

Ю

При поступлении такта считывания он свободна проходит на вход счетчика 4, и счетчик 1 переключается до тех пор, пока его содержимое не станет равно содержимо-

Il му счетчика 6. При одинаковых состояниях счетчиков на выходе компаратора 5 устанав ливается высокий потенциал, разрешающий прохождение следующего такта считывания через элемент И 11, переключение триггера 1 2 в нулевое состояние и остановку @ счетчика 4, При этом такт считывания, переключаю ший триггер 12, на счетчик 4 не проходит, так как низкий потенциал триггера 12 поступает на вход элемента И 2 раньше, чем такт считывания проходит через элемент задержки .1. С триггера 12 на его выход поступает сигнал об отсутствии информации в нако пителе 15. При поступлении такта записи триггер 12 переключается в единичное состояние и разблокирует вход счетчика 4 и дешифратора 13„

Kai только содержимое счетчика 6 доотигиет максимального значения (накопитель 15 заполнен информацией), срабатывает элемент:И 7 и переключает триггер

10 в единичное состояние.

Если содержимое счетчика 4 станет рав

-но содержимому счетчика 6 и тоже примет . максимальное эйачение, то сигнал с выхода элемента И 3 перебрасывает триггер 10 в нулевое состояние.

Если следующий такт записи приходит раньше, чем содержимое. счетчиков 4 и 6

-сравняется,, То через элемент И 8 он пере ключает триггер 9 в единичное состояние, дешифратор 14 блокируется и на выход устройства поступает сигнал переполнения.

При этом счетчик 6 не блокируется, и. после того, как с вся информация иэ накопителя 15 будет считана, счетчик 6 вновь записывает поступающую информацию по заранее определенным адресам, т.е. за время переполнения независимо от числа поступив-: ших на вход тактов записи потеря адреса записи и наложение избыточной информации на ранее записанную информацию не происходят.

Формула изобретения

Буферное запоминающее устройство, содержащее счетчики импульсов считывания и записи, первые выходы которых подключены через дешифраторы считывания и записи ко входам накопителя, вторые выходы соединены со входами компаратора, элемент задержки, подключенный через первый элемент И ко входу счетчика импульсов считывания, третьи выходы которого соединены со вторым элементом И, третий, четвертый и пятый элементы И, триггеры и тактовые шины записи и считывания, о т л и ч а ю щ е е с я тем, что, с пелью упрощения и повышения

> надежности устройства, выход втаоого элемента И подключен к нулевым входам первого и второго триггеров; третьи выходы счеч чика импульсов записи через третий элемент

И подключены к единичному входу второго триггера, прямой выход которого через чет583478

Составитель, В. Рудаков

Редактор Л. Утехина:, Техред Е. давыдович Корректор С. Гарасиняк

Заказ 4899/56 Тираж 729 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений н открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5 филиал ППП Патент, r. Ужгород, ул. Проектная, 4 вертый элемент И соединен с единичным входом первого триггера; входы пятого элемента И подключены соответственно к выходам компаратора, к тактовой шине считывания и инверсному выходувтороготрйггера, а выход пятого элемента И соединен с нулевым входом третьего триггера; инверсный выход первого триггера и прямой выход третьего триггера соединены соответственно с блокирующими входами дешифраторов 10 записи и считывания; тактовая шина записи подключена ко входам счетчика импульсов записи и четвертого элемента И и к единичному входу третьего триггера.

Источники информации, принятые во внимание при экспертизе:

1. Авторское свидетельство СССР

Ио 446052, M. Кл. 9 06 F 5/00, 1973 г.

2.;Патент США J4 3648247, кл. 340-172.5, 1972.