Параллельный однофазный регистр

Иллюстрации

Показать всеРеферат

Союз Советскин

Социа пист ииескик рыик

ОП И и 583480 (61) дополнительное к авт, свид-ву (22) Заявлено 04. 02.7 6 (21) 232 14 37/ (51) M. Кл.

G 11 С 19/00 с присоединением заявки №вЂ” (23) ПриоритетГааударатаеянай наюнтет

Ввета ВЬенатраа СОР на делаю нзабретеннй н атер@тай (43) Опубликовано 05. 12.77. Бюллетень (45) Лата опубликования описания 20.1 (ЬЗ) УДК 666.327. . 66 (O S8. 8) (72) Авторы изобретения

:A. И, Бухштаб, В, И. Варшавский, Блад. Б. Марахэвский,,Вяч. Б. Мараховский, В, A. Песчанский, Л. Я. Роэенблюм, Н. А. Стародубцев и Б. С. Пирлин

Государственное союзное конструкторско-технологическое бюро по проектированию счетных машин о (71) Заявитель (54) ПАРАЛЛЕЛЪНЫЙ ОДНОФАЗНЫЙ,;РЕГИСТР

Изобретение относится к области вычислительной техники.

Известей параллельный однсфазный регистр, содержаший ячейки памяти и логические элементы И-НЕ (11. Его недостатком 5 является низкая надежность.

Наиболее близким по технической сушности к изобретению являетс параллельный однофазный регистр, соцержаший ячейки памяти, первые управпяюшие входы Которых l0 подключены к выходу элемента НЕ, вход которого соединен со вторыми управляюшими входами ячеек памяти и управляющей шиной регистра $2).

Этот регистр также недостаточно надежен,!5

Белью изобретения является повышение надежности регистра, Поставленная цель достигается тем, что предложенный регистр содержит управляюший триггер, выход которого подключен к 20 выходной шине регистра, а его входы соединены с выходами ячеек памяти и элемента

НЕ, и тем, что ячейка памяти содержит элемент НЕ, элемент И-HE и элемент И-ИЛИНЕ с функциональными расширителями по И, 25 выход которого соединен со входом элемента НЕ, а входы подключены к разрядной информационной шине регистра, первому управляюшему входу ячейки памяти и выходу элемента НЕ, соединенному с первым выходом ячейки памяти и первым входом элемента

И-НЕ, другие входы которого подключены к разрядной информационной шине регистра и второму управляюшему входу ячейки памяти, второй выход, которой соединен с выходом элемента И-НЕ, а также тем, что управляюший триггер содержит элемент НЕ и элемент И-ИЛИ-НЕ с функциональными расширителями по И, выход которого подключен ко входу элемента НЕ, а входы подключены ко входам управляюшего триггера и выходу элемента НЕ, соединенному с выходом управ» ляюшего триггера и выходной шиной регистра.

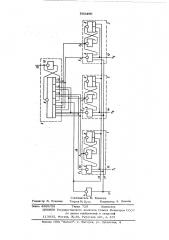

На чертеже представлена схема регистра.

Параллельный однофазный регистр содержит ячейки 1-3 памяти, элемент НЕ 4 и управляюший триггер 5.

Каждая ячейка памяти содержит элемент

И-HE 6, элемент НЕ 7 и элемент И-ИЛИ583480

ill= .8 с функциональными расширителями по

И.

Управляющий триггер 5 содержит элемент

И-ИЛИ-НЕ 9 с функциональными расширителями по И и элемент HE 10. 5

Вход элемента HE 4 соединен с управляющей шиной 11 регистра, а выход элемента НЕ 10 - с выходной шиной 12. Первый вход элемента И-НЕ 6 ячейки памяти соединен с выходом элемента HE 7, а его дру- Ю гие входы - с соответствующей из разрядных информационных шин 13-15, и управляющей шиной 11 регистра. Выходы эпементовИ-НЕ и НЕ 7 каждой ячейки памяти являются парафазными выходамн М,X Хк, «М

Х, Х, Х соответствующих разрядов регистра. ячейка памяти имеет первый 16 и второй 17 управляющие входы и первый 18 и второй 19 выходы.

Устройство работает следующим образом. iO

Перед поступлением входных сигналов на шины 13-15 ячеек на них подаются соответствующие уровню логической единицы сигналы, т.е. в исходном состоянии х = Y =

sf = 1, а сигнал на шине 11 соответствует 25 уровню логического нуля.

При этом сигнал на выходах элементов

НЕ 4,7 и 10 и элемента И-HE 6 соответствует уровню логической к единицы, а сит нал на выходах элементов И-ИЛИ-НЕ 8 и 30

9 - уровню логического нуля. Затем на шины 13-15 ячеек памяти поступают коды вводимого числа, а на управляющую шину

ll - сигнал уровня логической единицы.

Если сигнал на разрядной информационной З5 шине одной из ячеек памяти соответствует уровню логической.единицы, то на выходе элемента И-НЕ 6 этой ячейки устанавливается уровень логического нуля (Х »0). Если сигнал на разрядной информационной ши- 40 не соответствует уровню логического нуля, то выходные сигналы элементов НЕ

7 и И-ИЛИ-НЕ 8 этой ячейки памяти изменяется на противоположные только при появлении на выходе элемента НЕ 4 уровня ло- 45 гического нуля. После установки во всех ячейках памяти элементов И-ME 6 и HE

7 в противоположные состояния (Х14%() и уровня логического нуля на выходе элемента HE 4, as выходе элемента И-ИЛИ-HE 9 устанавливается сигнал логической единицы, а на выходе элемента HE 10 - сигнал логического нуля, что свидетельствует об окончании переходных процессов при записи кода в регистр.

Сброс регистра осуществляется следующим образом.

На разрядные информационные шины

13-15 ячеек памяти подаются сигналы уровней логической единицы, а на управляющую ® (шину 11 - сигнал уровня логического нуля.

Если в одной из ячеек памяти бап записан код единицы, т.е.@=1, 3(0, то на выходе элемента И-НЕ 6 этой ячейки устанавпивается уровень логической единицы Я 1), что свидетельствует о сбросе данной ячей-: ки памяти. Если в одной иэ ячеек памяти бып записан код нуля, то выходные сигналы элементов НЕ 7 и И-ИЛИ-КЕ 8 этой ячейки изменятся на противоположные лишь после появления уровня логической единицы на выходе элемента НЕ 4. После установки во всех ячейках памяти элементов И-НЕ B и HE 7 в противоположные состояния и

1 уровня логической единицы на выходе эйе»мента НЕ 4 на выходе элемента -Hl1H-НЕ

9 устанавливается сигнал логического нуля, а на выходе элемента HE 10 - сигнаа логической единицы,.что свидетельствует об окончании переходных процессов при сбро» се регистра.

Таким образом,. при управлении с помо щью выходного сигнала шины 12 пропессом записи информации в регистр и его сброса устраняется влияние разбросов задержек ло ,гических элементов, т.е. повышается надежность регистра.

Формула изобретения

1. Параллельный однофазный регистр, со»держащий ячейки памяти, первые управляющие входы которых подключены к выходу элемента НЕ, вход которого соединен со вторыми управляющими входами ячеек памяти и управпяюшей шиной регистра, о т л и чаюшийся тем, что,сцепьюповы щения надежности регистра, он содержит управляющий триггер, выход которого подключен к выходной шине регистра, а его входы соединены с выходами ячеек памяти и элемента ME.

2. Регистр по и. 1, о т п и ч а ю ш и и с я тем, что ячейка памяти содержит эпе» мент НЕ, элемент И-НЕ и элемент И-ИЛИ»

HE с функциональными расширитепями по И, выход которого соединен со входом эпемента НЕ, а входы подключены к разрядной информационной шине регистра, первому управляющему входу ячейки памяти и выходу элемента НЕ, соединенному с первым выходом ячейки памяти и первым входом эпемен та И-НЕ, другие входы которого подключены к разрядной информационной шине регистра и второму управпяюшему входу ячейки памяти, второй выход которой соединен с вы ходом элемента И-НЕ..

3. Регнстрпоп, l,отпичающийс я тем, что управляющий триггер содержит

583480 элемент НЕ и элемент И-ИЛИ-НЕ с фуикаьональными расширителями по И, выход кото» рого подключен ко входу элемента НЕ, à «ходы подключены ко входам у равляюшего триггера и выходу элемента НЕ, соединенному

«выходом управлякецего триггера н выход ной шиной регистра.

Источники информации, принятые во внимание при экспертизе:

1. Заявка М 1.378.199 Великобритания кл, С ll С 7/00, 1974.

2. Букреев И. Н. и др. Микроэлектронные схемы цифромп устройств. М., Советское радио, 1975, с. 63.

583480

Составитель В. Ковалев

Редактор Л. Утехина TexpeqМ.IIyna Корректор А Лакида

Заказ 4899/56 Тираж 729 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, r. Ужгорол, ул. Проектная, 4