Компенсационный стабилизатор постоянного напряжения

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

11Ц 584290

Сок1з Советских

Социалистических реслтблик (61) Дополнительное к авт. свид-ву (22) Заявлено 13.02.75 (21) 2104745/24-07 с присоединением заявки № (23) Приоритет (43) Опубликовано 15.12.77. Бюллетень № 46 (45) Дата опубликования описания 06.01.78 (51) М. Кл. G 05F 1/46

Государственный комитет

Совета Министров СССР ло делам изобретений и открытий (53) УДК 621.316.722. .1 (088.8) (72) Автор изобретения

}O. Н. Кузнецов (71) Заявитель (54) КОМПЕНСАЦИОННЫЙ СТАБИЛИЗАТОР ПОСТОЯННОГО

НАПРЯЖЕНИЯ

Изобретение относится к устройствам для электропитания радиоустройств.

Известны компенсационные стабилизаторы постоянного напряжения, содержащие последовательный регулирующий транзистор и схему сравнения, совмещенную с усилителем посто11нпого тока и источником 0110pHOl о постоянного напряжс, в качестве которого используется полупроводниковый стабилитрон (17

Наиболее близким к изобретению техническим решением является компенсационный стабилизатор постоянного напряжения, содержащий последовательный регулирующий транзистор, управляющим входом соединенный с коллектором усилительного транзистора, база которого подключена к резисторному делителю, соединенному с выводами для подключения нагрузки, а в эмиттерную цепь включен источник опорного напряжения (27.

Однако наличие резисторного делителя уменьшает величину приращения выходного напряжения, поступающую на базу усилительного транзистора. Вследствие этого ослабляется регулирующее действие стабилизатора, снижается коэффициент стабилизации и увеличивается выходное сопротивление.

Увеличение коэффициента стабилизации путем уменьшения сопротивлений резисторного делителя приводит к увеличению начального тока потребления стабилизатора и снижению его КПД.

Целью изобретения является повышение коэффициента стабилизации и КПД и уменьшение выходного сопротивления стабилизатора. Это достигается тем, что в эмиттерную цепь усилительного транзистора предлагаемого стабилизатора включен прибор с отрицательным сопротивлением.

1ð В качестве прибора с отрицательным сопротивлением может быть использован транзистор в режиме лавинного пробоя, переход эмиттер-коллектор которого включен в эмиттерную цепь усилительного транзистора, а

15 база через резистор соединена с коллектором.

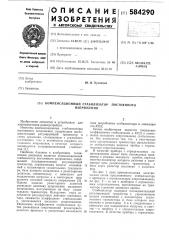

На фиг. 1 дана принципиальная электрическая схема предложенного стабилизатора с прибором с отрицательным сопротивлением;

2Р на фиг. 2 — то же с прибором с отрицательным сопротивлением, выполненным на транзисторе в режиме лавинного пробоя.

Стабилизатор содержит последовательный регулирующий транзистор 1, управляющим

25 входом соединенный с коллектором усилительного транзистора 2, база которого подключена к резисторам 3 и 4, соединенным с выводами для подключения нагрузки, а эмиттер — к прибору 5 с отрицательным сопроЗр тпвлением, В качестве прибора с отрицатель584290 ным сопротпвлcIl lñì Mîæñò быть использован транзистор б в режиме лавинного пробоя (см. фиг. ?), переход эмиттер-коллектор которого включен в эмиттерную цепь усилительного транзистора 2, а база через резистор

7 соединена с коллектором.

Стабилизатор работает следующим образом.

Увеличение входного напряжения или уменьшение тока нагрузки приводит к увеличению выходного напряжения. Это приращение выходного напряжения, ослабленное резисторным делителем 8, увеличивает базовый ток усилительного транзистора 2 и, соответственно, его коллекторный и эмиттерный токи. Увеличение тока эмиттера приводит к уменьшению падения напряжения на приборе 5 с отрицательным сопротивлением.

Это эквивалентно дополнительному увеличению приращения напряжения резисторного делителя 8, увеличению базового и коллекторного токов усилительного транзистора 2 и, следовательно, увеличению воздействия на последовательный регулирующий транзистор

1. Этим компенсируется дестабилизирующее действие резисторного делителя 8, что обеспечивает повышение коэффициента стабилизации и уменьшение выходного сопротивления стабилизатора.

Возмо>кность использования высокоомпого резисторного делителя 8 для уменьшения коэффициента стабилизации позволяет уменьшить начальный ток стабилизатора и повысить его КПД. Величина отрицательного сопротивления может регулироваться при помощи резистора 7. Включение в эмиттерцую

IN. ïü усилгггельного транзистора прибора с отрицательным сопротивлением по=.íîëÿåò повысить коэффициент стабилизации и КПД и уменьшить выходное сопротивление стабилизатора.

Формула изобретения

1. Компенсационный стабилизатор постоянного напряжения, содержащий последова1р тельный регулирующий транзистор, управляющим входом соединенный с коллектором усилительного транзистора, база которого подключена к резисторному делителю, соединенному с выводами для подключения на15 грузки, отличающийся тем, что, с целью повышения коэффициента стабилизации и

КПД и уменьшения выходного сопротивления, в эмиттерную цепь усилительного транзистора включен прибор с отрицательным со20 противлением.

2. Стабилизатор по п. 1, о тл и ч а ю щи и с я тем, что в качестве прибора с отрицательным сопротивлением использован транзистор в режиме лавинного пробоя, переход эмиттер25 коллектор которого включен в эмиттерную цепь усилительного транзистора, а база через резистор соединена с коллектором.

Источники информации, принятые во внимание при экспертизе

30 1. Книга «Источники электропитания на полупроводниковых приборах» под ред.

С. Д. Додика и Е. И. (ольперина. М., 1969, с. 101, рис. I П.

2. Карпов В. И. Полупроводниковые ком35 пенсационные стабилизаторы напряжения и тока. «Энергия», 1972, с. 42, 584290

11!! (!

1 ! ! ! фиг 2

Составитель 10. Морозов

Техред И. Михайлова Корректор H. Федорова

Редактор А. Пейсоченко

Заказ 2722/3

Подписное

Типография, пр. Сапунова, 2

Изд. № 1001 Тираж 1109

НПО Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5