Устройство для решения уравнения математической физики

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ 11ц 584314

ИЗОБРЕТЕНИЯ

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 07.07.76 (21) 2379721/18-24 с присоединением заявки № (51) М, КлР 6 06G 7/32

Государственный комитет

Совета Министров СССР ло делам изобретений и открытий (23) Приоритет (43) Опубликовано 15.12.77. Бюллетень № 46 (53) УДК 681.333(088.8) (45) Дата опубликования описания 10.02.78 (72) Авторы изобретения

М. М. Максимов,,Р. Л. Танкелевич и Я. И. Тетельбаум

Всесоюзный нефтегазовый научно-исследовательский институт (71) Заявитель (54) УСТРОЙСТВО ДЛЯ РЕШЕНИЯ УРАВНЕНИЙ

МАТЕМАТИЧЕСКОЙ ФИЗИКИ

Изобретение относится к вычислительной технике и предназначено для решения уравне ний .математической, физики.

Известны устройства, содержащие .циф ровые однородные конечно-разностные сеточные модели (1). Наиболее близким к изобретению по технической сущности является устройст во для;решения уравнения теплопроводности, содержащее цифровую однородную zoнечно-разностную сеточную модель (2). Одна ко известное устройство не обеспечивает достаточной точности решения уравнений математической физики.

Целью изобретения является повышение точности решения уравнений. В описываемом устройстве это достигается тем, что в него .введены блок управления и блок индикации параметров, и каждый узел сеточной модели содержит 1микропроцессор, блок памяти и <регистры, причем каждый выход блока упра вления связан со входом соответствующего микропроцессора, один вы«од каждого из которых подключен,к одному ll3 в«одов блока лнди7<ации параметров решения, а другие выходы каждого микропроцессора соединены с адресной и информационной шинами и со входами блока памяти и ретистров соот ветствующего узла сеточной модели, первый вход ре|гистров и:блока памяти соединены с информационными шинами, .вторые входы блока памяти и двух рсгистров соединены с адресной шиной, информационныс и адресные шины узлов сеточной модели соединены между собой и подключены соответственно к выходам блока управления и в«одам блока индикации.

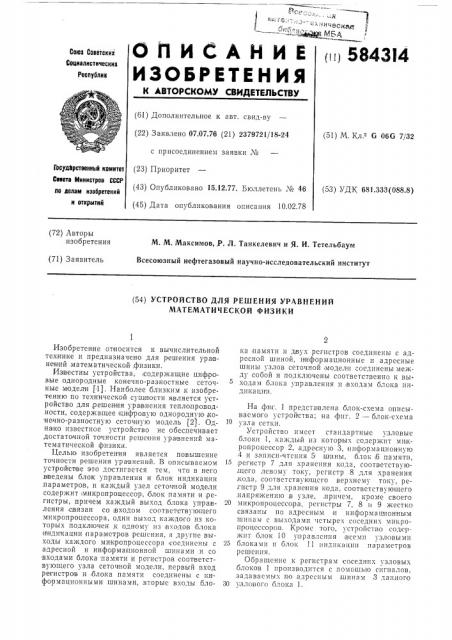

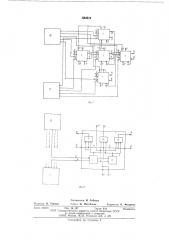

На фнг. 1 представлена блок-схема опнсываемово устрой ства; на фнг. 2 — блок-с«ема

10 узла сетки.

Устройство имеет стандартныс узловые б 70I

4 и записи-чтения 5 шины, блок (6 памяти, 15 рсгистр 7 для «рансння кода, соответствую,щего левому току, регистр 8 для хранения ,кода, соответствующего вер«нему току, регистр 9 для «ранения кода, соответствующего .напряжению в узле,,причем, кроме своего

20 микропроцессора, регистры 7, 8 и 9 жестко связаны по адресным и информационным шинам с вы«одами четыре«соседник микропроцессоров. Кроме того, i стройство содержит блок 10 у прав7сния всеми узловыми

25 блоками н блок 11 нн7нкацнн параметров решения.

Обращение к регистрам соседних узловых блока в 1 произBîäèTся с помошью сигналов, задавасмы«по адресным .шинам 3 данного

30 узлового блока 1.

584314

Работа устройства поясняется на примере решения нелинейной краевой задачи двухфазной фильтрации. Устройство описывается в терминах электрической сетки, являющейся универсальной моделью различных физических процсссов.

Предварительная область решения разбивается на подобласти, размерность которых соответствует размерности физического поля микропроцессоров. В информационном поле блока памяти каждого микропроцсссора храI:ÿòñÿ номер решаемой подобласти и тскушее значение потенциала в данной точке. Пеоед началом решения задачи по сигналу блока управления в информационном поле разгружается массив начальных значений искомых потенциалов. Все узловые блоки 1 устройства одновременно в соответствии с сигналами из блока yIlp авления выполняют однотипные операции в процессе решения задачи.

В начальный момент времени из инфо рмационного,поля выбирается по текущему,нОмеру подобласти значенис потенциала и засылается по сигналу «Запись» в регистры 9 всех микропроцессоров, затем по сигналу

«Чтение» код из регистра 9 левого микропроцессора засылается во внутренний регистр микропроцессора. После этого в другой внутренний регистр микропроцессора засылается код из своего регистра 9. Микропроцессор производит вычитание кодов напряжений

U,, U;-> и U;„, а затем умножение на проводимость Gx;Ä; кодовое значение которой хранится в ячейке блока .памяти. Сформированное значение кода левого тока 4 по сигналу

«Запись» записывается в регистр 7 для каждого микропроцессора. Аналогично формируется значение кода верхнего тока. Образовавшийся ток 4 засылается по сигналу записи:в регистр 8 микропроцессора. Код, соответствующий току., из регистра 7 нижнего микропроцессора поступает на внутренний регистр микропроцессора. На другой внутренний регистр микропроцессора подается код, соответствующий току из регистра 7 .правого микропроцессора, и произ водится их сложение. .К полученной величине прибавляется значение кодов из регистра 7 и регистра 8 для формирования значения невязки в;, "V Х Iii

1=1 4 = / + =1).

Из,внутреннего регистра микропроцессора

А-1 напряжение Uij записывается в соответствующую подобласть информационного поля и пересылается;на регистр 9.

Таким образом, все микоопроцессоры одновременно формируют новое значение кодов потенциалов в узлах до установления величин е меньше ".àäàííîãо значения. После этого все микропроцессоры переходят к вычислению значений G., и 6 ло .программе вычисления нелинейностей для обеих фаз рассматриваемого процесса и насыщенностей указанных фаз, х ранящейся в блоке памяти и результаты .передаются в ЦВМ и на блок индикации параметров.

Ф о р мула изо бр ет единия

Устройство для решения уравнений математической физики, содержащее однородную цифровую конечно-разностную сеточную модель, отличающееся тем, что, с целью повышения точности решения уравнений, в него введены блок управления и блок индикации параметров, и каждыЙ узел сеточной модели содержит микропроцессор, блок па,р мяти и регистры., причем каждый .выход блока управления связан со,входом соответствующего микропроцессора, один выход каждого из .которых подключен к одному из входо в блока индикации параметров решения, а другие выходы каждого микропроцессора соединены с адресной и информационной шинами и со входами блока памяти и регистров соответствующего узла сеточной модели, первые входы регистро в и блока памяти соеди4р нены с информационными шинами Вторые ,входы блока, памяти и двух регистров соединены с адресной шиной, информационные и адрссныс шины узлов сеточной модели соединены,между собой и подключены соответ45 сгвснно к выходам блока управления и Входам блока индикации.

Источники информации, прпнятыс во внимание:при экспертизе

5О 1. Авторское свидетсльство СССР № 510725, кл, G 06G 7/48, 1976.

2. Авторское свидстельство СССР № 494751, кл. G 06G 7/56, 1974.

884314 т ! !

1 !

Puz 2

Составитель И, Лебедев

Техрсд И. Михайлова

Редактор Л. Т.орина

Корректор Н. Федорова

Заказ 3252/4 Изд. № 187 Тираж 818

НПО Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, )К-35, Раушская наб., д, 4/5

Подписное

Типография, пр. Сапунова. 2!

v! (1

1 ъ !