Параллельный сумматор

Иллюстрации

Показать всеРеферат

Сфюа Советсини

Сациалистическик

Реснубпии (ll) 585494 (5l) М. Мл.

6 06 $ 7/385

Гввиврвтввввыя ввввтвт

Ввввтв Мнввтрвв 66ВР вв двввв взвбрвтвввб в втврытвй (53) У ® 681.325.5 (088.8) (72) Авторы изобретения

A,È.Æóðàâëåâ и В.С.Хасленников (7l) Заявитель

Особое конструкторское бюро вычислительной техники

Рязанского радиотехнического института (54) ПАРАЛЛЕЛЬНЫЙ СУММАТОР

ОП И

ИЗОБ

К АВТОРСКО (61) Дополнитель

{22) Заявлено 09, с присоединение (23) Приоритет (43) Опубликован (45) Дата опубли изобретение относится к области вычислительной техники и предназначено для использования в узлах ЭВМ и цифровой автоматики.

Известны параллельные двоичные сумматоры накапливающего типа со сквозным переносом, содержащее триггерный регистр, элементы И и ИЛИ, образующие схемы формирования собственных переносов, поразрядных сумм и сквозных пере- 10 носов 1б.

Существенным недостатком таких сумматоров является их критичность к дли» тельности тактовых импульсов.

Известен параллельный сумматор, со- g держащий в каждом разряде счетный триггер, выполненный на триггерах с разделительными входами, элементы И и ИЛИ, причем первые входы первого и второго элементов И соединены соответ- я0 ственно с первой и второй тактовыми шинами, а вторые входы — соответственно с входом разряда слагаемого и с входом переноса из младшего разряда, выходы их подключены к входам первогп элемента ИЛИ, выход которого подключен к входу счетного триггера, вход разряда слагаемого соединен с первым входом третьего элемента И, ;второй, вход которого соединен с выхо- З0

2 дом первого триггера с раздельными входами, а выход — с первым входом второго элемента ИЛИ, второй вход которого соединен с выходом четвертого элемента И, первый вход которого соединен с входом переноса из младшего разряда, а второй вход — с инверсным выходом первого триггера с раздельными входами, выход третьего триггера с раздельными входами является выходом данного разряда сумматора 12).

Функционирование известного устрой» ства может сопровождаться явлением состязаний, вызванных разбросами длительностей срабатывания входящих в сумматор элементов и возникающих в переходные периоды в структуре устройства.

Целью изобретения является повьввение помехоустройчивости устройства.

Достигается это тем, что третий вход третьего элемента И соединен с инверсным выходом второго триггера с раздельными входами.

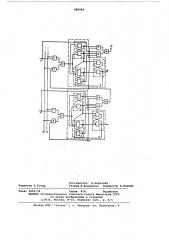

На чертеже приведена схема двух разрядов параллельного сумматора.

Предлагаемое устройство содержит элементы И 1 и 2, элемент ИЛИ 3, счет ный триггер 4, выполненный на триггерах 5, б и 7 с раздельными входами, 585494 каждый иэ которых выполнен из двух элементов И-НЕ, элементы И 8 и 9 и элемент ИЛИ 10 °

Первая тактовая шина 11 подключена первому входу элемента И 1, вторая тактовая шина 12 — к первому входу элемента И 2. Вторые входы элементов

И 1 и 2 соединены соответственно q входом разряда слагаемого 13, с входами элементов И 8 и 9 и с входом переноса из младшего разряда 14. С выхода элемента ИЛИ 10 снимается сигнал переноса из данного разряда 15. Сигнал суммы снимается с прямого выхода триггера 7.

l6

Суммирование чисел осуществляется в два такта. В первом такте формируются поразрядные суммы Si и переносы С сформированные непосредственно в 4

ых разрядах и происходит.,распространение переносов вдоль цепи сквозного 20 переноса, состоящей из элементов И 8, 9 и ИЛИ 10.

Во втором такте переносы, распространявшиеся вдоль цепи сквозного переноса, поступают на входы счетных Щ триггеров соответствующих разрядов сумматора и изменяют их состояние.

Поскольку информационные управляющие сигналы с инверсного выхода триггеров 6 в момент тактового воздейст- 80 вия не изменяются, то между разрядами сумматора исключены состязания входящих в него элементов.

Формула изоьретения

Параллельный сумматор, содержащий в каждом разряде счетный триггер, выполненный на триггерах с раздельными входами, элементы И и ИЛИ, причем первые входы первого и второго элементов И соединены соответственно с первой и второй тактовыми шинами, а вторые входы — соответственно с входом разряда слагаемого и с входом переноса из младшего разряда, выходы их подключены к входам первого элемента ИЛИ, выход которого подключен к входу счетного триггера, вход разряда слагаемого соединен с первым входом третьего элемента И, второй вход которого соединен с выходом первого триггера с раздельными входами, а выход — c первым входом второго элемента ИЛИ, второй вход которого соединен с выходом четвертого элемента И, первый вход которого соедиíен с входом переноса из младшего разряда, а второй вход— с инверсным выходом первого триггера с раздельными входами, выход третьего триггера с раздельными входами является выходом данного разряда сумматора, отличающийся тем, что, с целью повьиаения помехоустойчивости сумматора, третий вход третьего элементами соедйнен с инверсным выхо : дом второго триггера с раздельными входаМи.

Источники информации, принятые во внимание при экспертизе

1. Папернов A.A. Логические основы ЦВТ, И., Советское радир, 1972, c. 159 рис. 14.

2. Авторское свидетельство СССР

9 510713, кл. а 06 F 7У385, 1973

595494

Составитель В .Березкин .

Техред ц.дндрейчук КорректоР A.Лакида

Редактор Е.Гочар

Заказ 5049/39 Тираж 818 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, r. Ужгород, ул. Проектная, 4